Hi team,

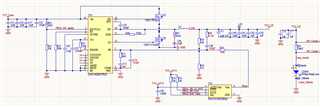

My schematic diagram of the circuit is as follows. I found that loweside mosfets were heating badly in heavy-duty mode, and measured LO output waveforms separately.

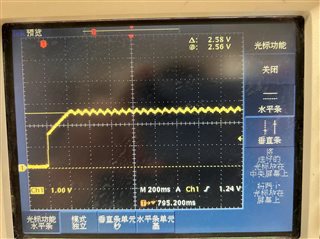

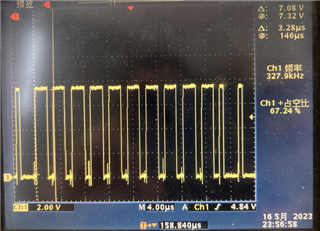

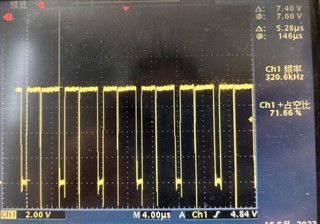

First of all, when the output voltage is 1.35v and the load current is 0.85A, the temperature of Q3 is 46℃ and the output waveform of LO is measured as follows, it can be seen that the opening time of Q3 is inconsistent, which is unreasonable

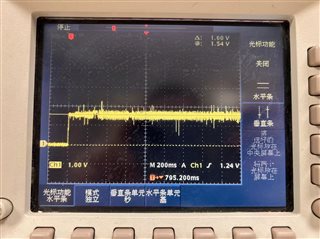

Then I adjusted the output voltage to 1.45V, the load current to 3.8A, and the temperature of Q3 rose to 100℃ within 10 seconds. At this time, the LO output waveform was measured as shown in the figure below, and it was found that the turn-on time side of lowside mosfet was longer.

when I have replaced LM5146, highside and lowside MosFeTs respectively. Serious fever still exists in Q3 under heavy load. Please help me analyze the cause.