Dear TIer,

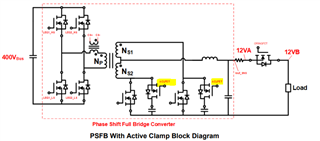

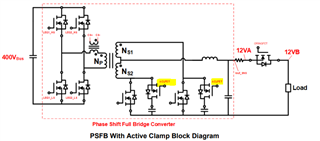

Could you help us provide some paper design note about PSFB with active clamp?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Dear TIer,

Could you help us provide some paper design note about PSFB with active clamp?

Hi Kuo,

I have asked the original designer to share some details, please give us some time.

Thanks,

Robert

/cfs-file/__key/communityserver-discussions-components-files/196/Active-Clamping-Calculations.xlsx

Hi Kuo,

I have attached an excel sheet that can help determine the appropriate clamp capacitance. For the design, we typically allow for some delay between the rising edge of the SR drain voltage and the turn-on of the ACL FET to allow the ACL FET to better achieve ZVS. I find it is easier to measure this on the bench and set the delay in the code (this is controlled by PSFB_ACL_DEADBAND_RED_INITIAL in the psfbpcmc_user_settings.h). You will also want to ensure that for peak current mode control, you are blanking the current measurement as the ACL will introduce some distortion to the transformer current. This means you need to ensure a minimum duty cycle to allow for the ACL to finish before observing the current for peak current mode control.

Best Regards,

Ben Lough