Hi,

I have some questions about the mode switching of UCD3138.I hope to receive the support of the TI team.

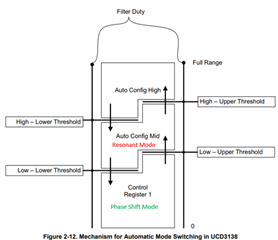

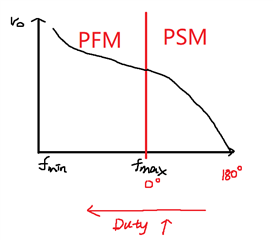

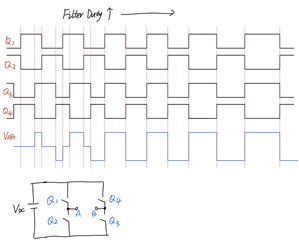

1. For phase shifting mode, when I set DPWM to open loop operation and the phase trigger is determined by the FILTER Duty.

I found that as the FILTER Duty increases, the phase between DPWM0A and DPWM1A also increases.

How to achieve a phase reduction between DPWM0A and DPWM1A with the increase of FILTER Duty?

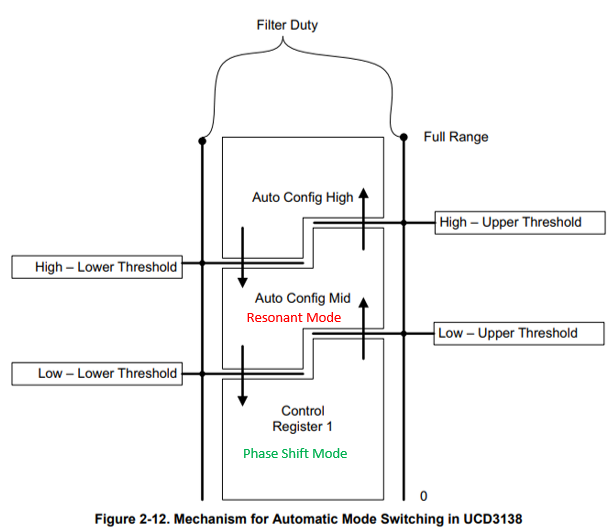

2. Will the previous working mode status be saved after the mode switch of DPWM?

For example, DPWM initially operates in phase shift mode, and enters variable duty cycle mode after DPWM0A and DPWM1A are shifted by 90 degrees.

Will the phase between DPWM0A and DPWM1A remain at 90 degrees after entering variable duty cycle mode?

3. For mode switching, changing the working mode of DPWM, etc., all are related registers of DPWM.

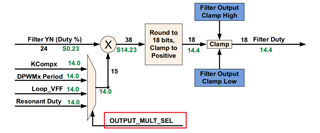

Can I change the register of the loop? For example, in different modes, the output YN of the filter will be multiplied by different coefficients.

Thank you very much again for TI's help.

Best Regards,

Jie