- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi

I have a query about BQ76930EVM

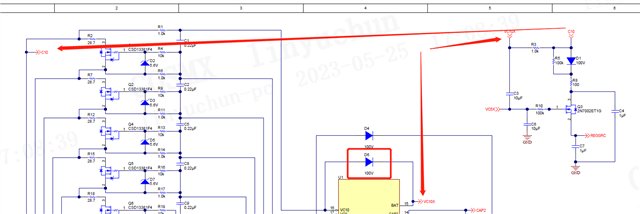

1, The role of R3 and C3 seems to be the same as that of D6. Can I remove D6 or R3 and C3?

2, What is the function of D42, Q33and Q36?

Waiting for your reply.

Thanks

Star

Hello Star,

1- R3 and C3 are part of the recommended filter components for the supply pins. See below for D6. More info can be found in this video

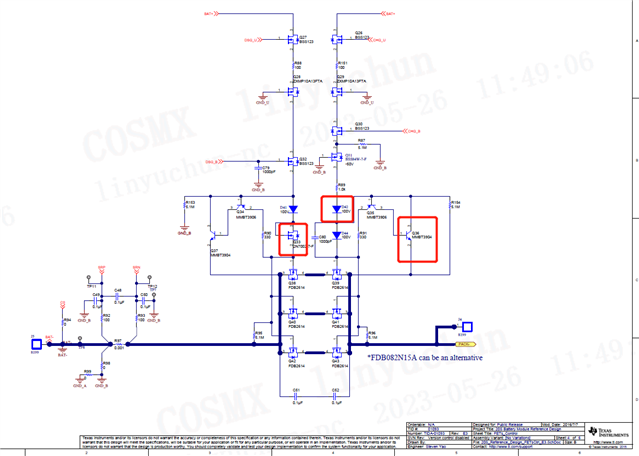

2- The purpose of Q33 is to add a voltage drop along with D41 to lower the voltage at the gates of Q38, Q40, and Q42 (this is explained in the Design guide). I would assume D42 is for the same purpose, to lower the gate voltage for Q39, Q41, Q43.

I will loop in the system engineer who created this reference design for questions on Q36.

Regards,

Jose Couso

The purpose of Q36 is to expedite to extract and exhaust the charges on the gate of Q39 so that the cut off speed of Q39 can be desired for actual application, adjusting the value of R91 can change the FET cut off speed.

Hi Steven

Thanks for your help.

Still have a query need your help.

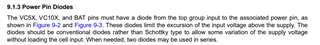

1, D6 is a flyback diode as described in page 27 of the EVM user guide www.ti.com/.../slvu924d.pdf

If the discharge FET turns off quickly with high current and with a large inductive load on the pack terminals, the inductance may create a high voltage on the PACK- terminal. D6 will limit the voltage to near the PACK- terminal.

how D6 limit the voltage to near the PACK- terminal?

2, Can I not use Q36, but connect PACK directly with pin 3 of Q35?

Waiting for your reply.

Thanks

Star

D6 will be forward biased when the discharge FET is turned off as the current would continue to flow from Pack- to Pack+ via D6, since it is forward biased, the Pack- voltage is clamped to Pack+, this is how Pack- voltage is limited.

I haven't tried with direct connecting Pin3 of Q35 to GND, suggest to make a simulation to check the result

Hi Steven

Thanks for your reply.

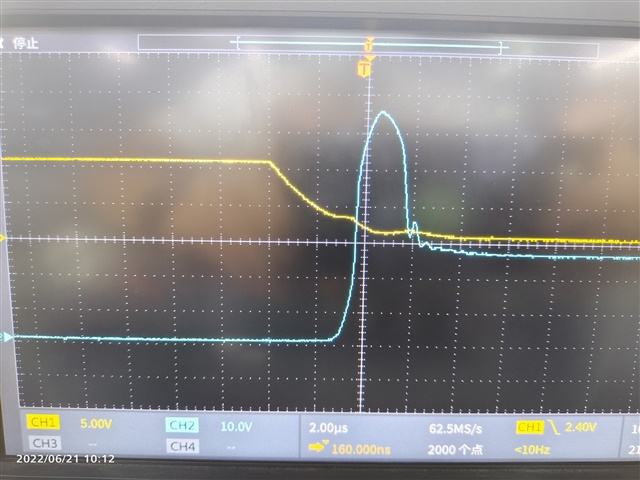

I did a short test, the BMS with D6, but the P- voltage was not clamped to BAT(I think it should be BAT instead of PACK+). the voltage of P- is double than BAT. Why?

Waiting for your reply.

Thanks

Star

Do you have the plot of short test, in the schematic of P29, Pack- shall be clamped to BATT+ when the discharge path is cut off, due to respond delay of D6, a brief high pulse on PACK- may be observed, but it should be quickly clamped by D6, D6 should be selected with appropriate forward clamping respond speed so that the brief pulse won't damage other components in the circuit.

Hi Steven

Thanks for your help.

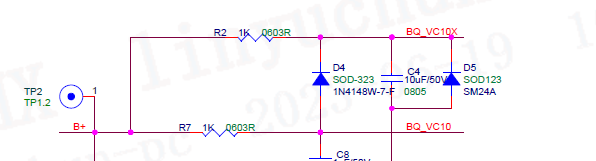

The waveform and schematic as below:

Thanks

Star

Looks like this could be caused by the output filter capacitor acting bootstrap capacitor before the charge on it has been discharged, do you have the waveform at cathode pin of the diode?