Hi Team,

I am using TPS546D24A in my design. I would like to get the circuit design get reviewed by experts.

Vin=5V

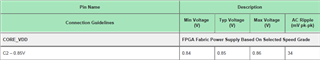

Vout=0.85V

Iout=120A

I also have few queries regarding the design of the IC.

1. What should be the VSEL resistor value for Vout=0.85V

2. How should the PMBus pins terminated if they are unused in the design.

3. How to terminate MSEL1,MSEL2,VSEL and ADDRSEL pins in stack follower ICs.

Regards,

Shifali N6332.TPS546D24A.pdf

alternate capacitor part number with better derating value.

alternate capacitor part number with better derating value.