Other Parts Discussed in Thread: TPS65262

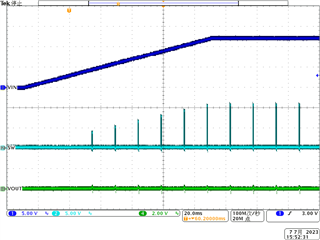

Is the buck overcurrent protection enabled during startup? The attached scope plot seems to indicate that overcurrent protection or some other fault is triggered, with a subsequent 14ms hiccup time (Buck1 3.3V rail is blue trace).

In general, during what phases of operation is the buck overcurrent protection enabled and disabled?

I'm looking for a transient based PSPICE simulation that can help verify peak currents during startup. Does TI have a solution for that?