Other Parts Discussed in Thread: UCC21710

Hi Team,

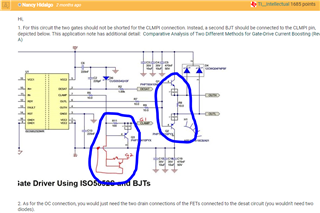

We have used UCC21710-Q1 for single SiC mosfet for our application. Now, we are planning to use same IC for 2 parallel SiC MOSFETs (G3R30MT12K). Can this IC used for 2 parallel SiC MOSFETs?

Please provide if you have any reference designs for 2 parallel SiC MOSFETs operation using UCC21710-Q1.

Thanks and Regards

Umamaheswararao