Other Parts Discussed in Thread: BQSTUDIO

Hi,

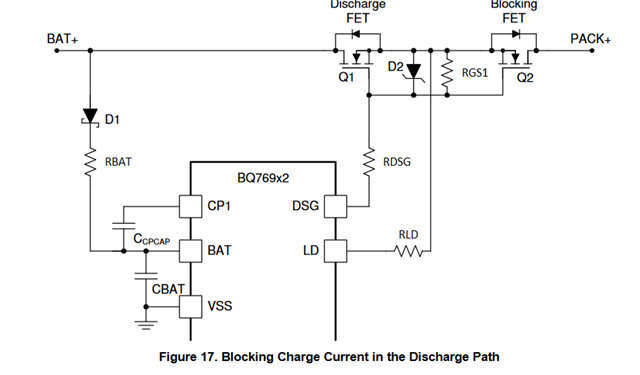

We're using the BQ76952 in a parallel FET configuration (we have Settings:FET:FET Options - SFET set to 0), and we're noticing strange behavior regarding the CFETOFF and DFETOFF pins. We're controlling these two pins via a microcontroller and both pins are configured to their alt functions (Settings:Configuration:CFETOFF/DFETOFF Pin Config both set to 0x2). Individually, these pins both function properly. If only one of the pins is high, the corresponding FET will indeed be off. However, in our firmware logic, when switching between charge or discharge mode, all of the charge/discharge circuitry is turned off before enabling the other side, so there will be a brief period where both CFETOFF and DFETOFF are high. However, this doesn't seem to be the case, and instead when CFETOFF and DFETOFF are both high, the discharge FET seems to stay on. I understand that in a series configuration, this would be expected behavior in order to protect the discharge FET, but why is this happening in parallel mode?