Other Parts Discussed in Thread: TPS65219

Hi

We are using PMIC TPS6521908 in our design.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi

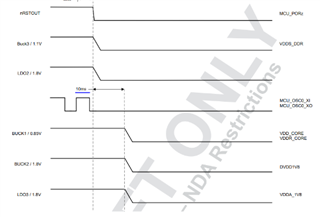

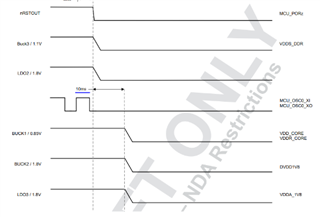

We are using PMIC TPS6521908 in our design.

Hi Premalatha,

The device expert is currently out of the office until tomorrow. They will look into this and provide a response when they return. Please expect a delay in response accordingly.

Thanks,

Field

Hi,

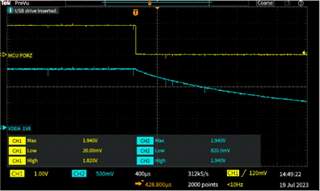

Thank You for using E2E! Based on the information provided in the previous message, the board #1 executes an orderly power-down sequence matching the TPS6521908 TRM and board #2 executes an immediate power-down with all rails turning OFF simultaneously. There are four key items that affect the power-down sequence: the voltage level on the pre-regulator that supplies VSYS, the external capacitance/load, the BYPASS_RAILS_DISCHARGED_CHECK register setting and any faults. Since the problem in your design seems to be more related to the sequencing order, then we could suspect the voltage on VSYS goes below the UVLO threshold before the PMIC completes the power-down sequence or the PMIC is detecting a fault during power-down.

Could you add the VSYS voltage to the scope captures in your previous message? Do you see any interrupt in the interrupt source register (INT_SOURCE, address 0x2B)?

To read the interrupt register you would have to pull the Enable pin back to high so PMIC can transition to Active state.

Thanks,

Brenda

Hi Brenda,

Thanks for your response. We had further discussions on this issue internally and got to know such a power down use case is not applicable w.r.t our design. Hence we haven't continued our analysis on this further, at this point of time.

Hi,

Thanks for sharing an update! If the information in my previous message answered your questions, feel free to click on the "resolved" option so we can close this ticket. You can always get back to the same ticket or submit a new one if additional support is needed.

Thanks,

Brenda

Hi Premalatha,

The device expert is currently out of the office until next week. They will look into this and get you a response when they return. Please expect a delay in their response accordingly.

Thanks,

Field

Hi,

Thanks for your patience! An immediate or orderly power-down does not affect the PMIC but might have consequences on the reliability of the processor. PMIC executes a sequenced power-down as long as the voltage on VSYS is present until the power-down sequence is complete. I would recommend checking with the processor team about the consequences (if any) of not following the expected power-down sequence from the AM62. Here is the link to the processor forum:

https://e2e.ti.com/support/processors-group/processors/f/processors-forum

Thanks,

Brenda