Hello TI expert,

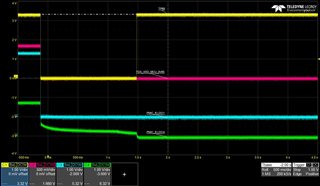

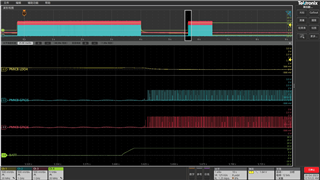

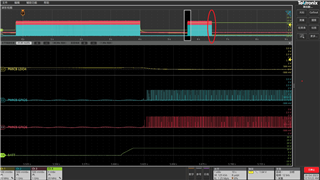

We use PDN_0C solution for TDA4 SOC. Currently we encountered a issue when PMIC is powered on.

Our ECU shall be about 1.5A @12V. However, for very few products,sometimes ECU may be about 47mA@12V when ECU is powered on.

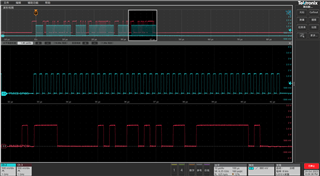

We try to find the root cause and find there is something wrong for PMICs. I test PMIC's pin and there is no output for PMICs while the power input is normal.

I try to reproduce it on the issue product for 3 times and dump all the registers of PMICs. I attached the logs here. Could you help review it and give your suggestions? Actually, there is something abnormal with the INT registers and others.