Hi,

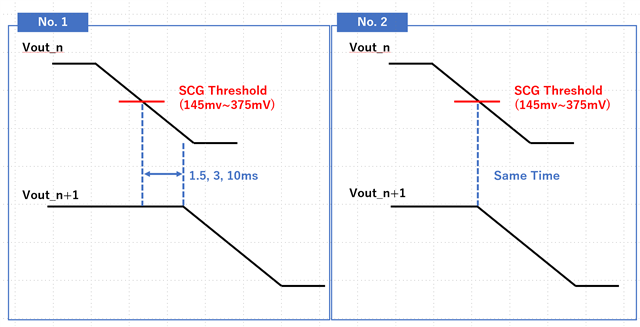

The following thread states that SCG is affecting the Power Down sequence.

According to my results, the timing of power down changed with the load current. Is it safe to assume that the desired power down sequence can be realized by setting the SCG when there is no load?

Best Regards,

Nishie