Other Parts Discussed in Thread: LM25149-Q1EVM-2100, LM5149-Q1, LM5149-Q1EVM-400

Hello,

I am currently in the process of constructing a buck converter with the following specifications:

Input Voltage: 15-80V

Output Voltage: 12.51V

Output Current: 10A (Maximum)

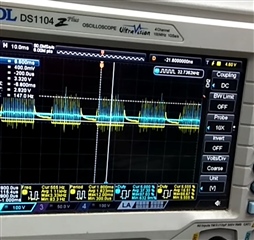

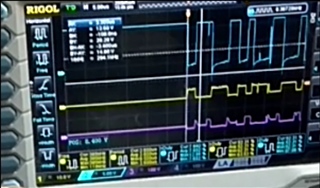

- During testing, I encountered the following issues:

1.The integrated circuit (IC) is getting damaged under both load and no-load conditions.

2.When I increase the voltage, the IC heats up and eventually gets damaged.

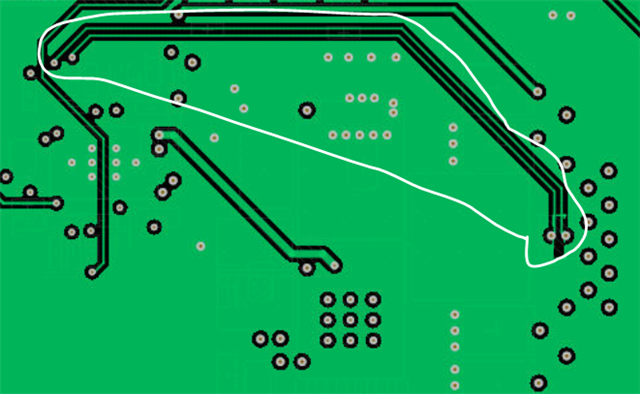

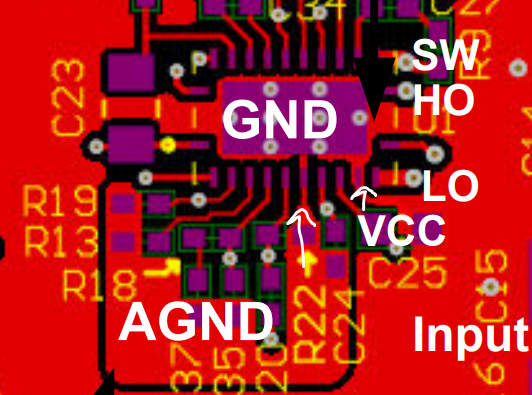

I have attached my schematic for your reference.

I am seeking suggestions for improvement and kindly request your support in resolving this issue.