Hello

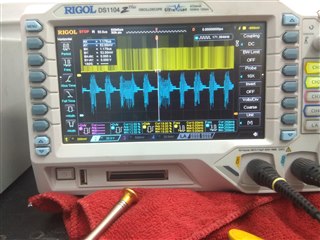

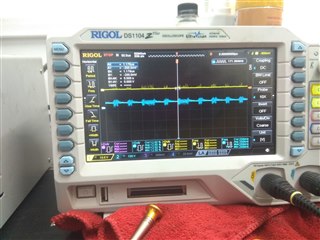

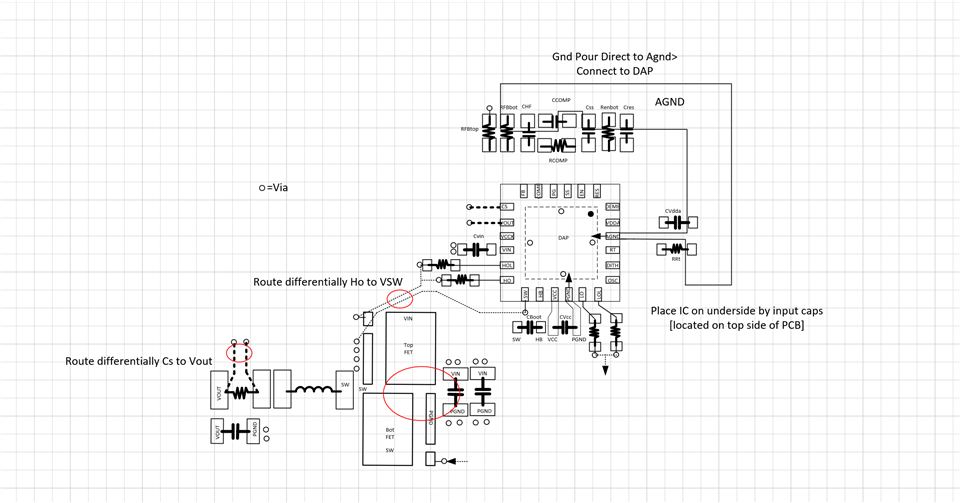

I have implemented modifications to my PCB board based on discussions in the TI forum. Nevertheless, the MOSFET is encountering damage on both the high and low sides, and the PWM waveform continues to be ungenerated. I have attached a photo of the PWM waveform for your review. I am seeking recommendations for appropriate MOSFETs for my design, in case my current MOSFET selection is incorrect. Additionally, I would appreciate insights on generating PWM without utilizing both MOSFETs or How can PWM will generate with MOSFETs. Furthermore, there is a discrepancy in the output voltage, as it is producing 8.5 volts instead of the intended 12V.