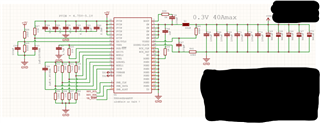

Our recent design has the main VR: TPS546D24ARVF, Vin=5V, Vout=0.295V,nom at 40A Imax.

Problem statement:

The VR is very noisy and leaking noise into clocks.

High level request:

The power design is straightforward and shouldn't have these issues. We implemented the design in WeBench and followed the design recommendations 100%. So before I look into design improvements, e.g. layout, I want to verify basic hw/sw configuration. (Sometimes it is one silly mistake or error that causes everything to not work!)

Specific requests:

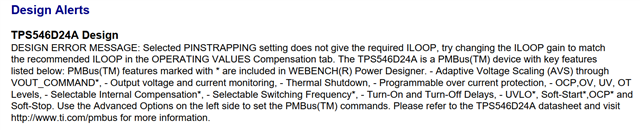

(1) Check for errors in WeBench recommendation, including passive values, resistor strap settings, etc. I uploaded the WeBench pdf.

(2) Configuration file vs. defaults? We had difficulty connecting through the TI Fusion GPIO/I2C dongle, so we have been using a Raspberry Pi for basic configuration through I2C. Our current methodology assumes the configuration defaults are "healthy" given the proper resistor strappings (e.g. MSEL,VSEL,ADRSEL). For example, the default frequency is 550 kHz (read from I2C), and this matches WeBench, so the default is OK. One of my concerns is there could be settings made when providing a config file with Fusion that we are not supplying since we are using the RPi, whether they are "hidden" settings or we are just missing them on our end.

(3) Noise leakage is occurring onto a UART Clock at ~3MHz, and a PLL Refclk at 20-40MHz.

I haven't done deep qualitative analysis on the noise, but it shows up in a scope capture of the clock (550kHz), and the UART is non-functional with the VR switching (even under light loads). Our workaround to get the board running is with an external EVM (we have systems working with the TPS546D24A and the TPS546B24A-2PH).

Thanks in advance for your help!