Other Parts Discussed in Thread: UCC21750, UCC21710

Hi Team,

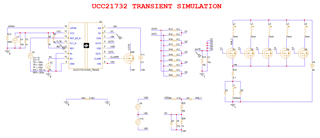

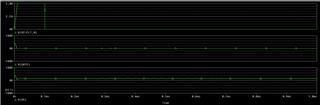

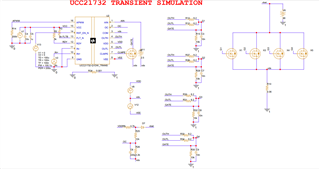

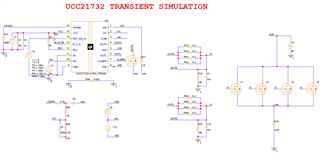

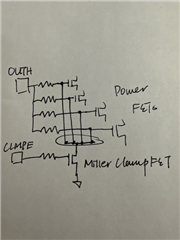

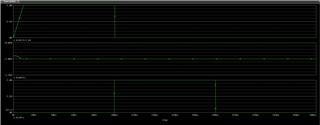

I'm currently working on Isolated gate driver design and I'm using UCC21732-Q1 to control the MOSFETs. While performing simulation in PSPICE, I see gate remains in HIGH state and FLT pin goes low when the IN+ changes the state from LOW to HIGH.

What might be the reason?

Any suggestions UCC21732-Q1DW_TRANSwould be appreciated.

Thanks.