- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello,

This is my first time fully designing an isolated power supply. I am struggling with managing all of the design constraints: magnetics, power, slope compensation, isolated feedback, etc.

I am having some difficulty understanding the full chain of events that controls the OUTA and OUTB duty cycling on the UCC28084. I will do my best to explain what I think is happening and any guidance or correction would be much appreciated.

The design I am trying to achieve is:

UCC28084

Power: 0.5 - 5.0 W (1.0 W nominal)

Vin: 12-48 V (24 V nominal)

Vout: Isolated 5 V (push-pull)

VDD: 10 V auxiliary supply provided from LM25019 (this is the voltage supplied to R.p that sets the CTRL voltage through the current from the output of the PS2801-1 opto-coupler)

f.sw = 600 kHz (I am hoping to adjust this for slope compensation / efficiency once my understanding is stronger)

Isolated type II feedback with TL431 and PS2808-1 opto-coupler (1.75 < CTR < 2.85 for 9 mA diode current, 10 mA into cathode of TL431 with 1 mA from a bias resistor)

Coilcraft HPH1-1400L with 4 windings on primary and 2 windings on secondary for turns ratio of 2:1

FDT86246 power switching MOSFETs

I used SLUA584A to set a reasonable value for R.f = 499 Ω (R.ramp) and R.CS = 1.13 Ω

I am trying to use many resources (TI SMPS Comp Made Easy, Ridley Designer Series XV: Designing with TL431, and many others)

To start my slope compensation I need to define the power stage first. I am having difficulty defining the gain A.vc of the power stage.

The way I understand it is the upward current ramp of the output buck inductor (referred to the primary) travels through the MOSFET and R.CS creating a voltage ramp

Additional 'downslope' voltage ramp is added from 5*I.set*R.f (in my case 150 uA * 499 Ω = 0.075 V)

This voltage ramp should peak below 0.47 V as the maximum input signal to the CS pin

This voltage ramp, +0.3 V (from the functional block diagram), is compared against the CTRL voltage * (60/(60+80) = 0.429*V.CTRL

One of the things I do not fully understand is that 0.47 V + 0.3 V = 0.77 V is the maximum CS input into the PWM comparator.

But that means my control voltage can't be larger than 0.77 / 0.429 = 1.80 V (is this true? If so my auxiliary supply of 10 V might be too large for the opto-coupler to bring the CTRL voltage low enough?)

Is the Current Sense Gain from the datasheet 1.9 < A < 2.5 V/V the equivalent of inverting the voltage divider on the CTRL signal? 1/0.429 = 2.33 So this is just accounting for 1% tolerance of the resistors?

What is the meaning of the CTRL to CS offset voltage in the datasheet? 0.70 V nominal (It would be silly to add this as an additional offset to the 0.3 Vref in the block diagram?)

I tried to organise this information as best I can, but with some of my holes in understanding I can read that I've rambled a bit. I hope this sheds some light on what level of understanding I have and someone can help me get the rest of the way there.

Thank you in advance for your time and comments. Kind regards,

Hi Kyle,

1. V_CTRL will be set by the optocoupler current to regulate output voltage (through the resistor between VDD and CTRL). 10V for your auxiliary is a good value.

2. Current sense gain is nothing but VCTRL/VCS. You can also estimate it with the voltage divider and +0.3V.

3. CTRL to CS offset is nothing but VCTRL when VCS=0V.

Thank you

Hello Manuel,

Thank you very much for your reply. If I may I just want to ask a couple clarifying questions:

This makes sense and agrees with my understanding. One issue I am having is knowing what steady state voltage on the CTRL pin sets my nominal output of 5.0 V. I tried running the UCC28084 in open-loop, with no opto-coupler feedback from the output, using a potentiometer between VCC and CTRL so see if I could find a CTRL voltage that brings my output value to 5.0 V. Is this the normal way to do this? I'm worried I might damage some of the components in open-loop, for example the push-pull configuration can have flux imbalance which current mode control is supposed to help prevent.

Hi Kyle,

If you want to test the IC in open loop, you can use a potentiometer from VCC. Make sure VDD is powered with a voltage higher than UVLO. Set you switching frequency fsw with RT resistor (check Datasheet). You can leave Iset floating and in the case of VCS pin you can connect a resistor from VCC (check typical value VCS in Datasheet).

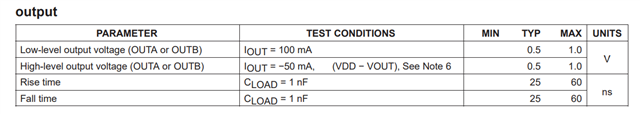

What you will expect is PWM pulses at the output A and B with 1V high state (see below) with a fsw set by RT.

Thank you.