Hi team,

Could you please answer questions below?

Question 1

Question regarding startup when TPS27S100 is ENABLEd

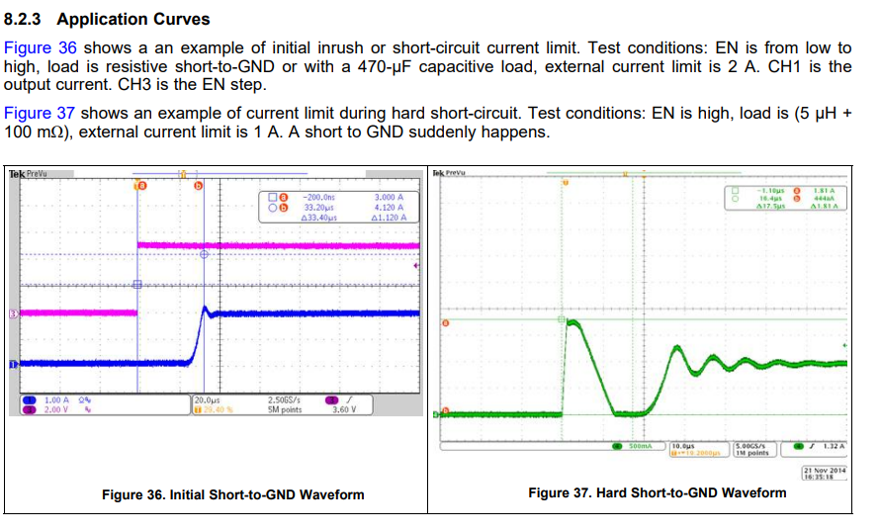

I believe that if you set a current limit value externally, it will clamp to that current value at startup.

In other words, if the current is limited to 2A externally, the rush current downstream immediately after ENABLE will be clamped to 2A. On the other hand, after the operation stabilizes after ENABLE, when the current reaches the current limit value, eFUSE turns OFF.

Question 2

Are there any regulations regarding the rise time on the output side when eFUSE is turned on?

I would like to know this to check the SOA due to inrush current when there is a FET downstream.

Thank you for your help.

Regards,

Taito Takemura