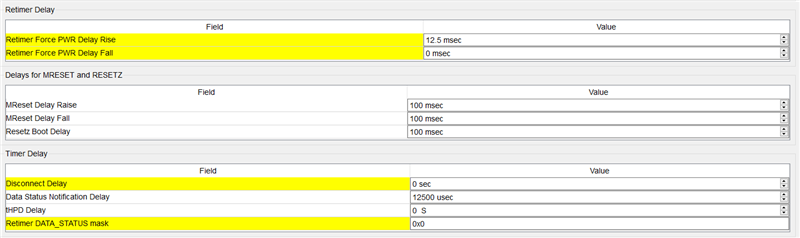

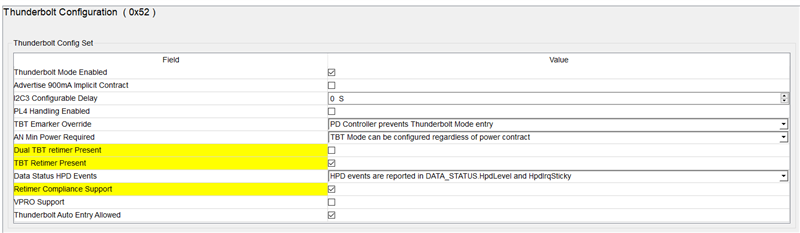

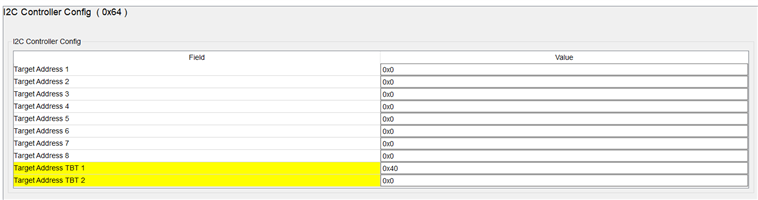

We are using the TPS65994AE on a Raptor Lake platform. Using the GUI, I've set the GPIO Config register under Port 1 seeting to control power to the retimer and to reset the retimer. What other key configuration settings are needed to work with a Burnside Bridge retimer?

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.