Other Parts Discussed in Thread: LM76202-Q1, LM5067

Hi Ti team,

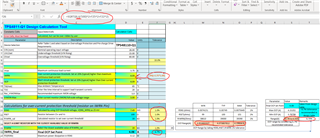

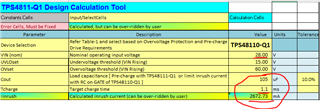

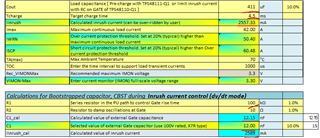

I want to consider TPS4811-Q1 in my circuit selection.But i have some doubts for the fitment.

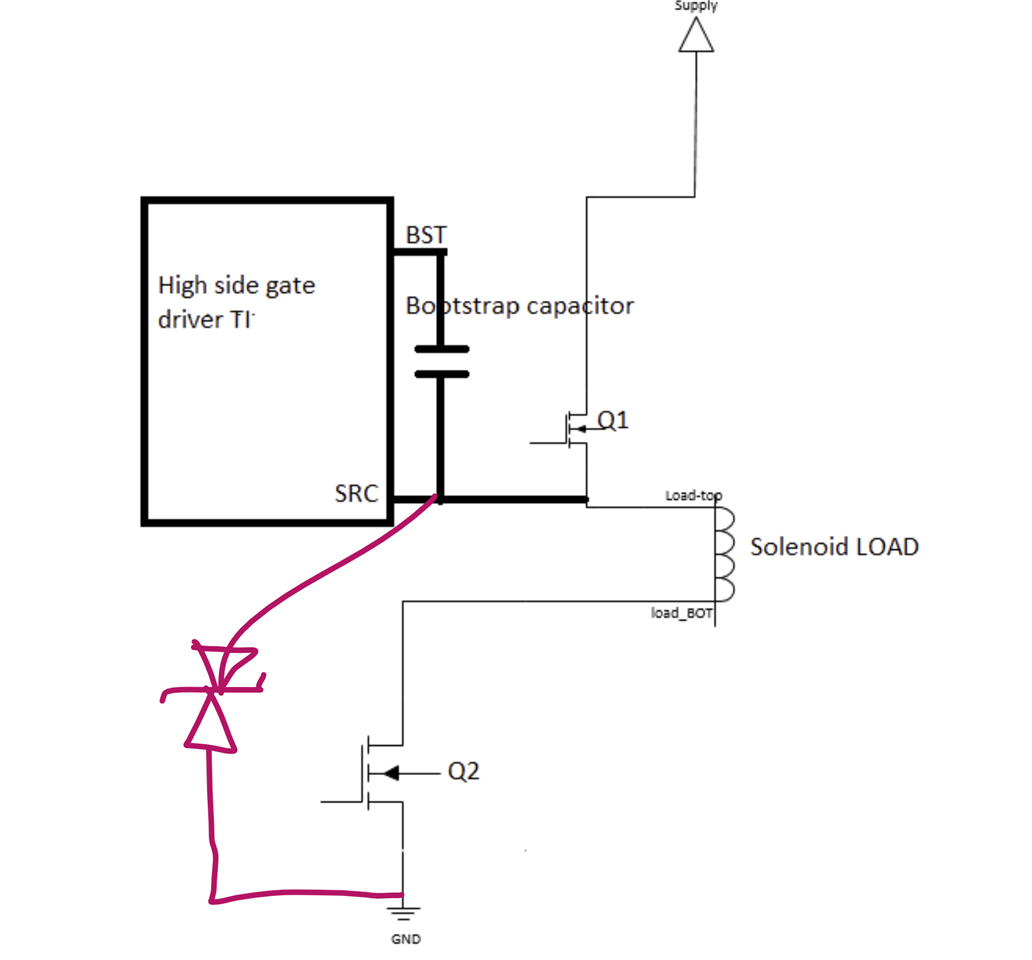

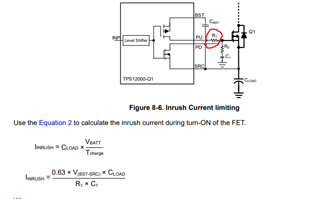

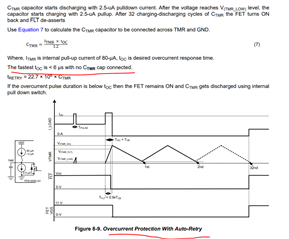

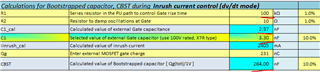

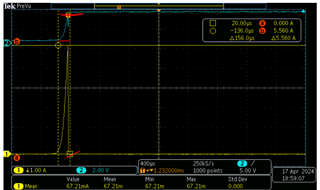

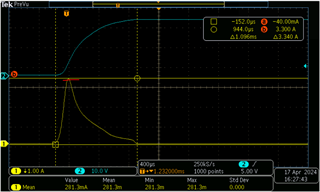

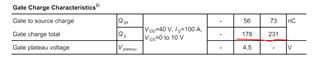

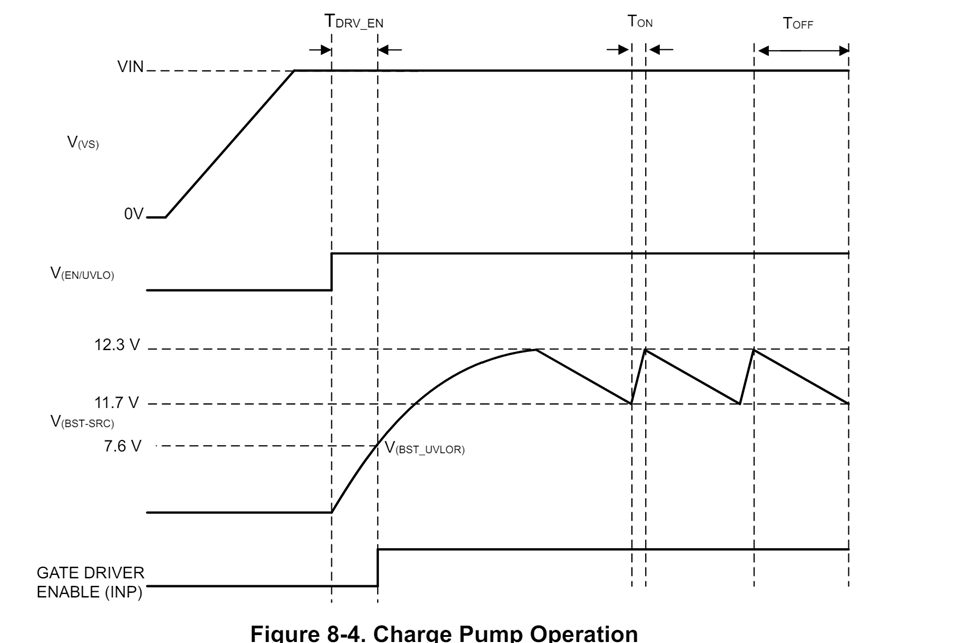

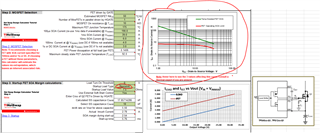

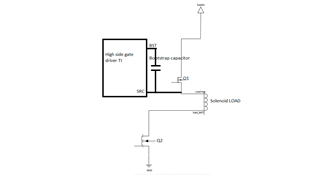

Q1 & Q2 MOSFETS i will operate at same time due to my application requirement. It is said that in TPS4811-Q1 datasheet internal gate driver charge pump of 12v will charge the BST capacitor.

But if i operate Q1 & Q2 at the same time is any problem to charge the BST capacitor.

My doubt is

I will not connect the BST capacitor. According to the internal gate driver architecture charge pump will supply the internal push -pull( PU,PD) TOTEMPOLE MOSFETS.

Can i connect PU,PD pin directly to my High side MOSFET gate in above picture.

Does my High side MOSFET can b drived/operated -ON/OFF without the BST capacitor .

can you please calrify my doubt or can you suggest me any solution to above doubt.

so that i can use this above gate driver for my application.

Thank you,