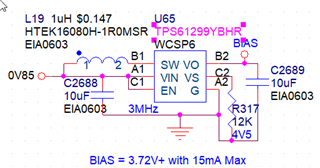

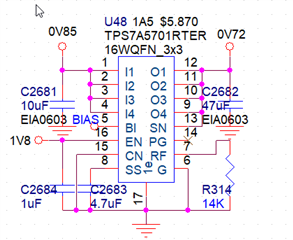

Other Parts Discussed in Thread: TPS7A57, TPS61299, TPS7A57EVM-056, TPSM82903EVM, TPS62122, TPS62120

Is there a part like TPS7A74 but without VBIAS requirement that can do VIN 1V1, VOUT 0V9 and current 1A or more?

So far I've only found LT3022 which is expensive and large. Thanks! - Patrick