Hi TI,

We use LM5177 as 9~48V DC input regulator. Here are our design parameter.

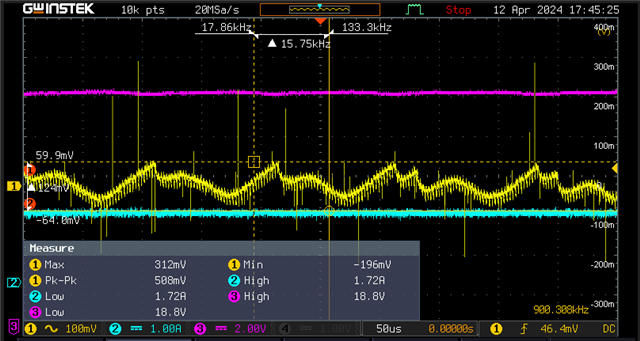

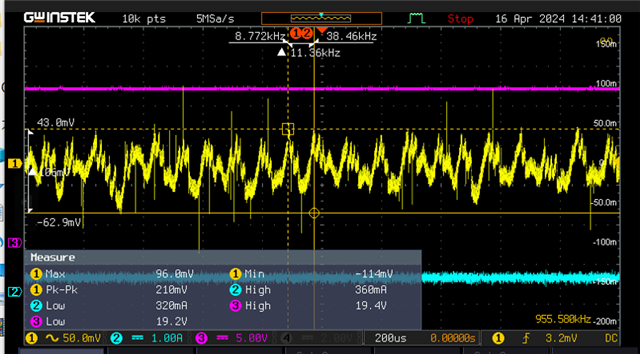

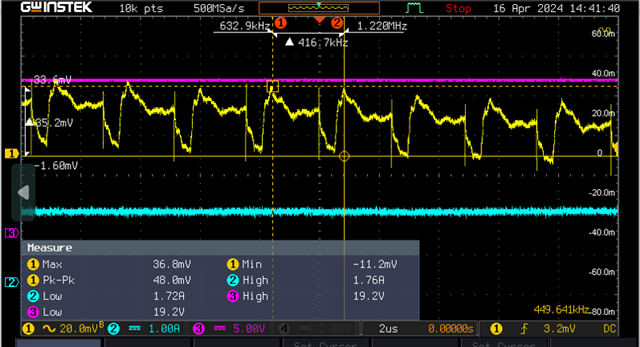

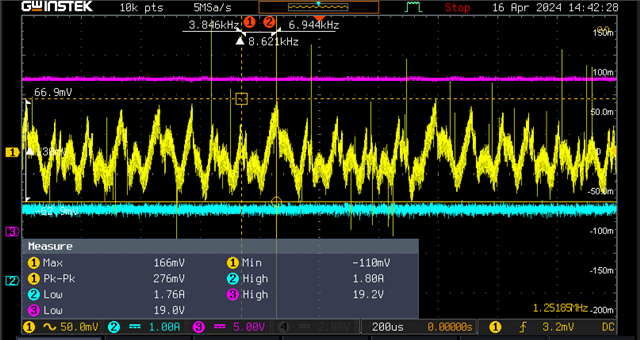

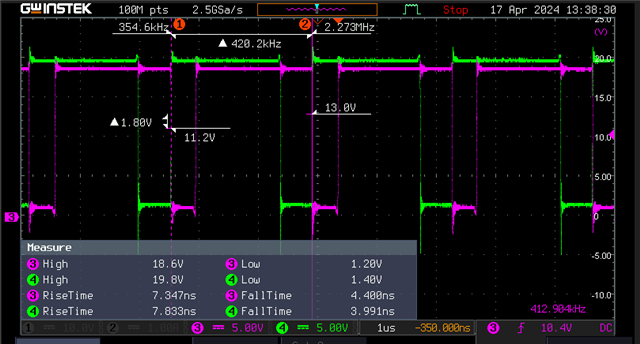

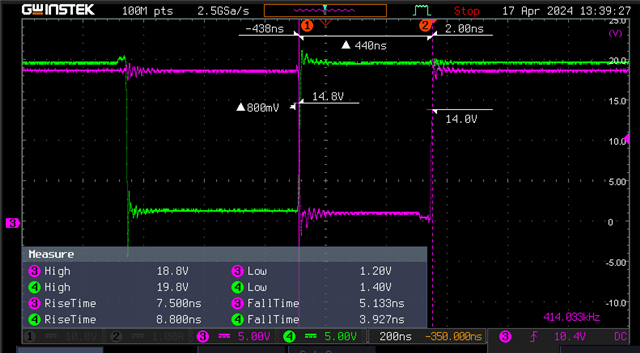

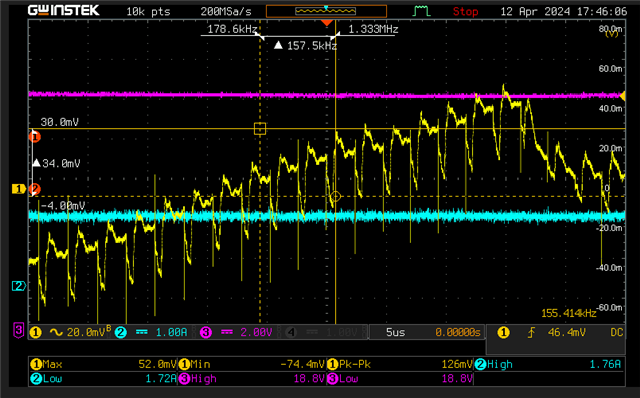

Base on our current setting, we can observe the low frequency ripple.

Are there any suggestions to optimize this low frequency ripple?

If I need to fine tune the compensation components, do you have any guieline to determine the crossover frequency and phase margin?

Fig 1. Ripple under 1.75A load

Fig 2. Low frequency Ripple under 1.75A load