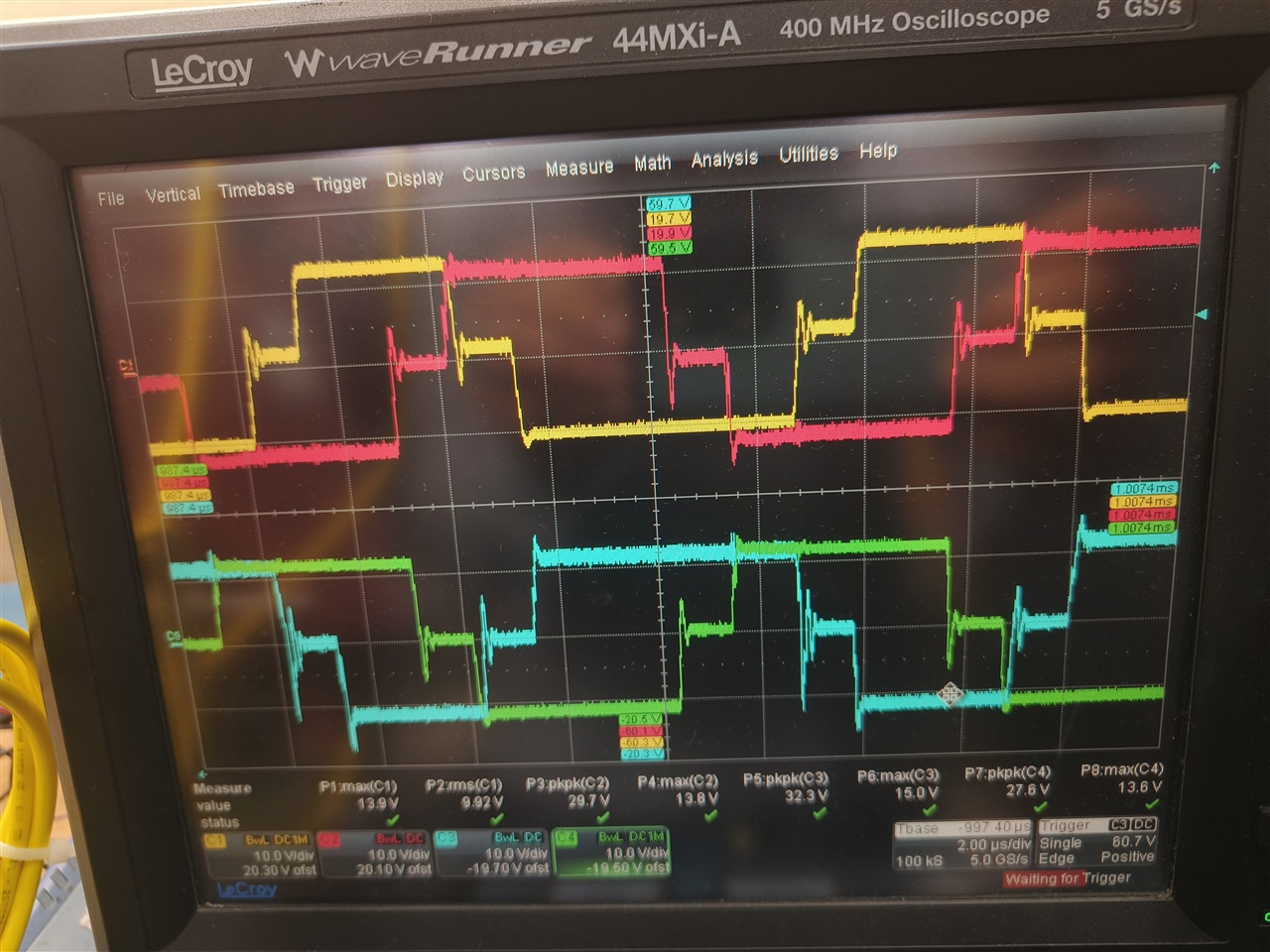

Other Parts Discussed in Thread: UCC28950

Hi Mike O' / Team,

I want to start testing the controller (UCC28951) which is assembled on the PCB. I'm Preparing a Testplan to start Testing. Kindly guide.

I want to Start off With NO LOAD condition, then slowly give Load current in Linear order.

My Max Load current is around 80A. and Minimum is 2A.

Tmin Resistor: 13K. Should i further reduce Tmin resistor value or is this correct?

In the datasheet section 7.3.9(Burst Mode), It says, If the controller is still demanding a duty cycle less than TMIN, then the controller goes into shut down mode.

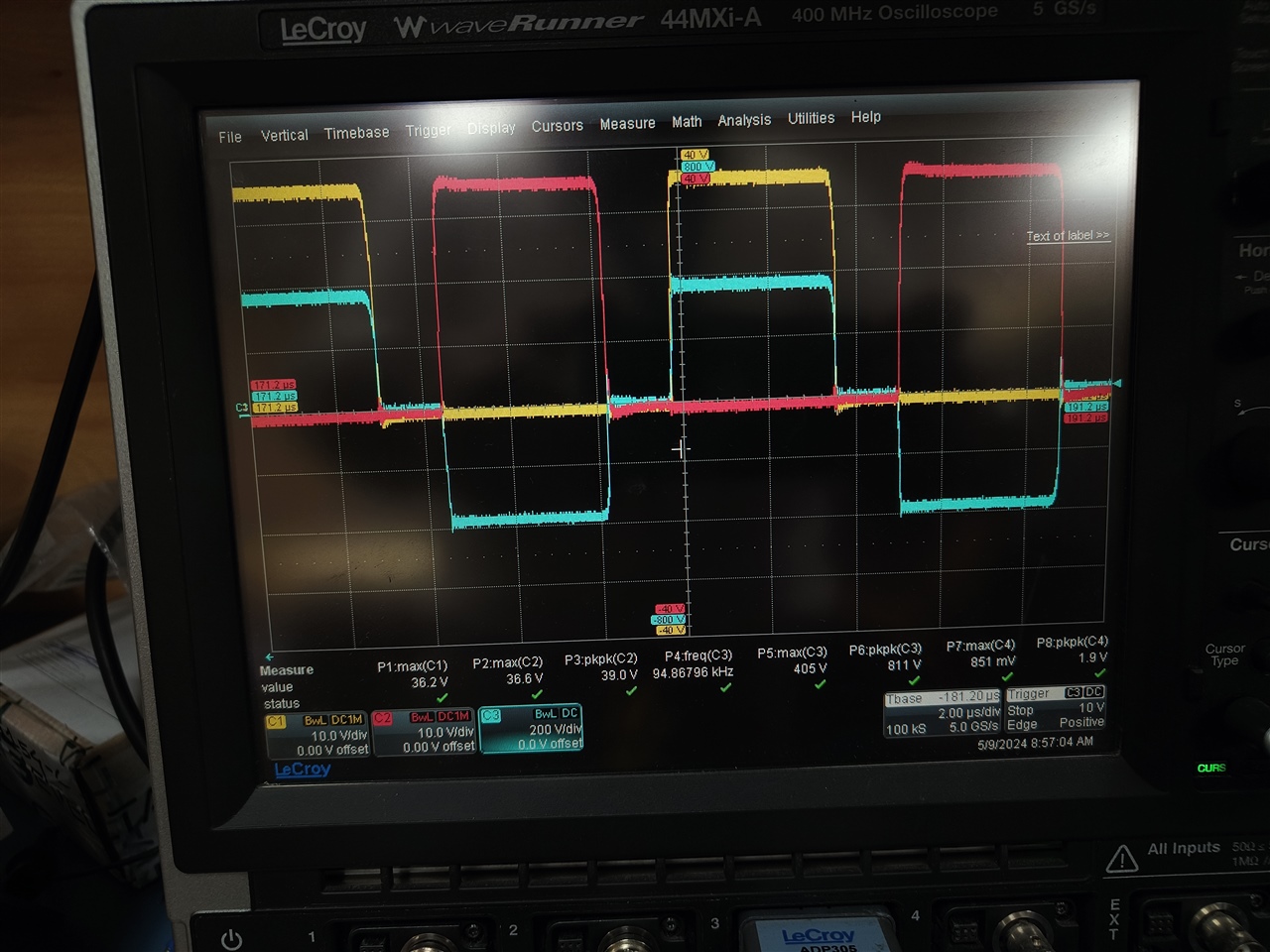

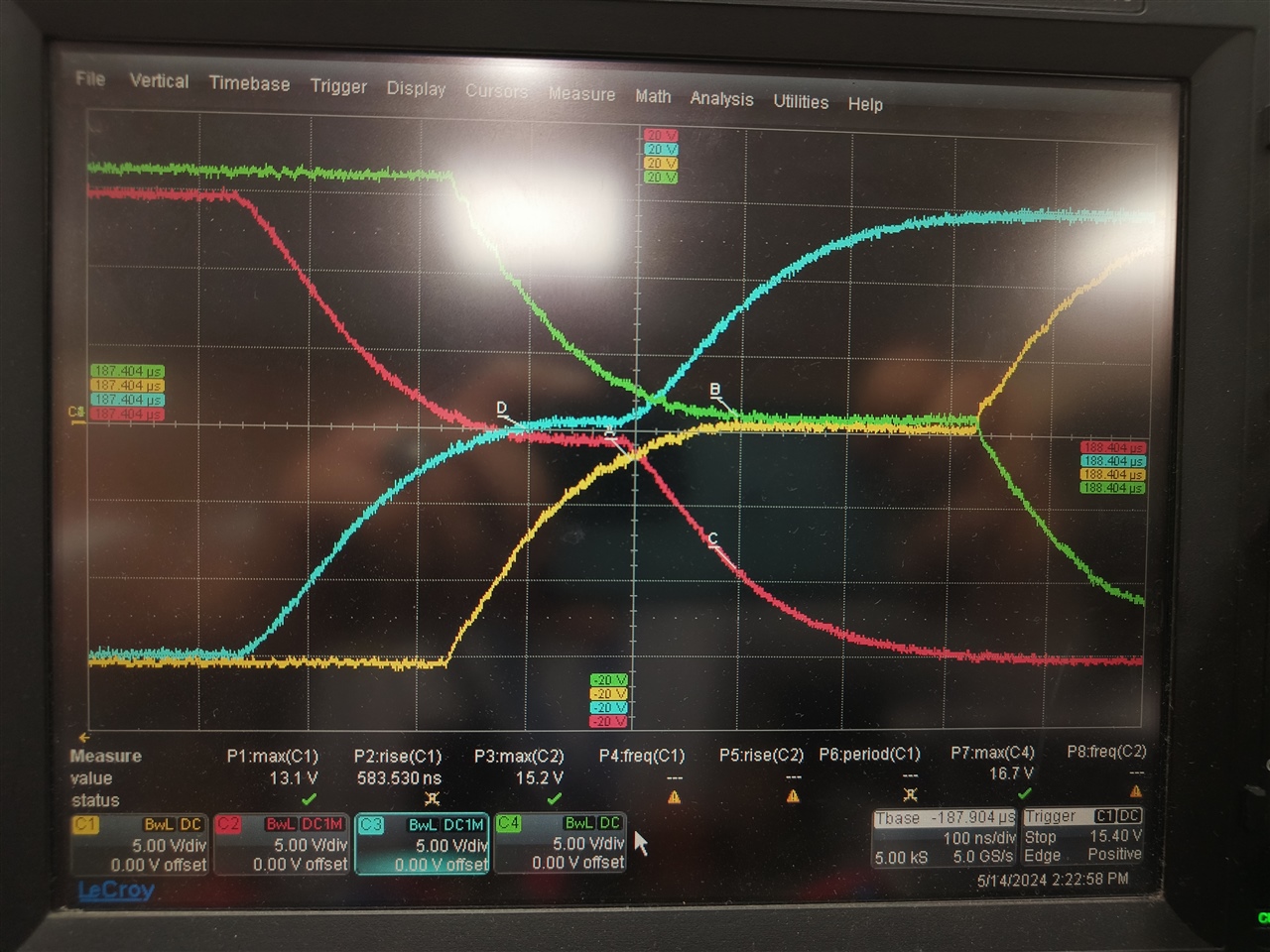

I'm Getting confused with the different modes of operation. As i Understand When the controller starts after SS/EN pin is released, the output voltage should be regulated with No load.

Then Let's say i give load current of 2A (it will be very light load conditions),

Then let's say I increase the Load current to 5A, it enters DCM mode or still be burst mode?

Further Increasing (Approx 10A in my case) less than 15% of load current which is huge as the FET diodes will heat up, It Will stay in DCM mode. Correct?

More than 15% of load current, The Controller enters CCM mode. I want to understand Whether my understanding of operation is current and what Tweakings / Value changes i may need to do while testing? Please guide.

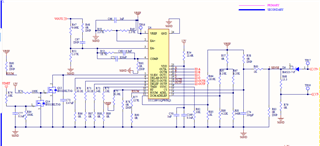

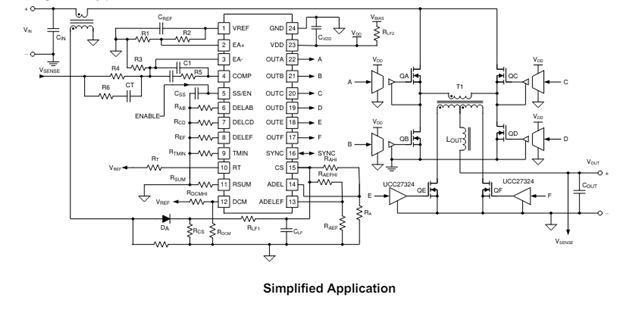

Find the circuit diagram Below.