Other Parts Discussed in Thread: UCC28950, UCC21551, PMP8740,

Team,

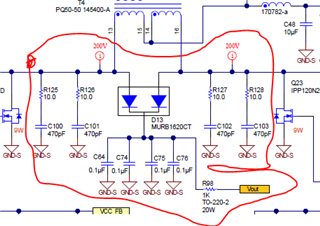

Taking inspiration and learning from 600W evaluation board.

Below are my design specs:

Model 1:

Input voltage - 200VDC ~ 600VDC

Output - 13VDC ( 84A max, 2A min)

Model 2:

Input voltage - 600VDC ~ 1000VDC

Output - 13VDC ( 84A max, 2A min)

I will have series of questions related to the design, I will keep posting in the same thread.

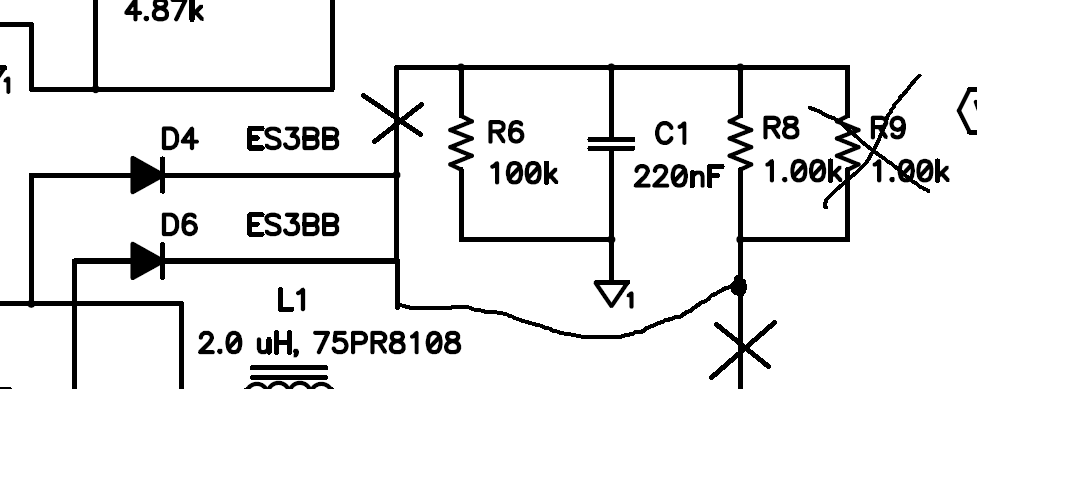

1. Planning to use gate drive transformer for both the models.

below are calculations for the same. Kindly review and advice

| Steps | Parameter | Value | Unit | Remarks |

| 1 | Peak Voltage (Vpk) | 15.00 | V | Gate driver voltage |

| 2 | Min Switching Frequency (Fs) | 98000 | Hz | Datasheet - UCC28950, excel design doc - SLUC222D |

| 3 | Time Period | 0.0000102 | S | T=1/f |

| 4 | Max Duty cycle ( nominal ) | 0.70 | % | Datasheet - UCC28950, excel design doc - SLUC222D |

| 5 | Ton | 0.00000714 | S | Max duty * Time period |

| 4 | Calculated ET | 0.00010714 | V-S | |

| Calculated ET ( micro ) | 107.14 | V-uS | ||

| 5 | Calculated ET for bipolar | 214.29 | V-uS | Ton=2*ET/Vpk, for Bipolar drive |

| 6 | Source Current Of Gate drive pin | 1 | A | Datasheet(UCC27324P) |

| 7 | Inductance Required | 0.0001071 | H | Ipk=UpkDmax/(Lprim,min*fmin). |

2. At steady state , will duty cycle be 50% or varying ? Since my duty cycle is varying from full load to light load, Burst Mode or No load, Is there anything to be taken care at the gate drive transformer side. Kindly advice.

3. selected gate driver for now GT04-111-315-B