Other Parts Discussed in Thread: TPSF12C1

hello,there have very good effect in low-voltage test, but no effect on high test,VINJ have many peak voltage,it is more than 12V

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

hello,there have very good effect in low-voltage test, but no effect on high test,VINJ have many peak voltage,it is more than 12V

I use TI's TPSF12C1Q filter board in my model,it is boost pfc +dcdc,Vinj is more than 12V near by model's input current zero crossing through ,Vinj is 7V in other time .I try to some ways and much time to solve this problem according to TPSF12C1Q datasheet,but it have no effect.can you provide your email to me in order to that i can send some picture to you and help me??thanks

Hi Jin,

You can add pictures to this thread. Click on "insert" and then "image/video/file". You can then upload the file.

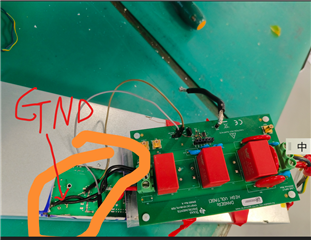

Have you tried increasing VIN to 15V? You mentioned that you have the filter board. Is it the one shown below?

If so, try increasing C6 and C7 on the filter board to 4.7nF or 10nF.

Please provide pictures of your setup and what is the switching frequency of the PFC?

Ben

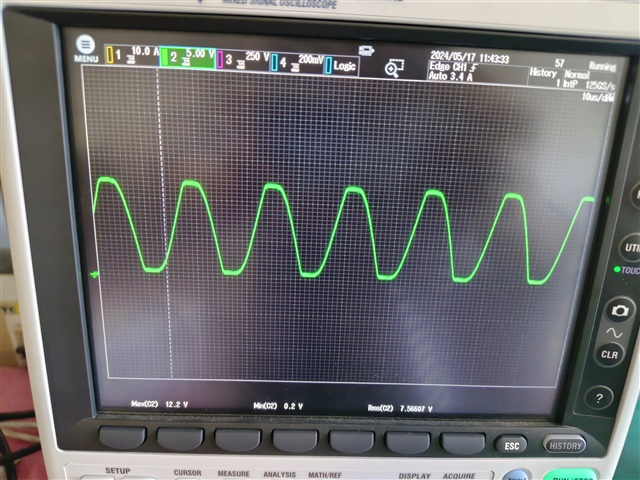

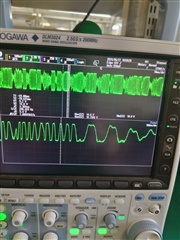

hello,yes,my filter board as your picture.C6 and C7?do you said inject capital or Y capital?C6 andC7 is Y capital in datasheet as picture 1, VDD is 12V, I will try to increase to15V,my PFC is 120kHz( old module PFC is 65kHz,Vinj is 12V in all time,so i change F from 65kHz to 120kHz),this is my test module and filter board as picture 2 ,i change some parameter as quickstart calculator,picture 3 is my wave of Vinj and input current(PFC 120kHz).please help me to solve this problem,thanks

TPSF12Cx-Q1_quickstart_calculator_A9(2)-CP3500,EMI CM choke to 9TS 17TS C13 8.2 C11 1.5.xlsm

TPSF12Cx-Q1_quickstart_calculator_A9(2)-CP3500,EMI CM choke to 9TS 17TS C13 8.2 C11 1.5.xlsm

TPSF12Cx-Q1_quickstart_calculator_A9(2)-CP3500,EMI CM choke to 9TS 17TS C13 8.2 C11 1.5.xlsm

Hi Jin,

The picture of your setup shows no chokes on the board. You can try increasing the Y-capacitances on the regulator side, which is C6 and C7. What kind of chokes are you using for your setup? Are they ferrite or nanocrystalline? Looking at your scope shots, the INJ pin does show it is saturating. Is the filter board GND grounded to the chassis case? Trying using the new BOM in the quickstart calculator below.

TPSF12Cx-Q1_quickstart_calculator_A9(2)-CP3500,EMI CM choke to 9TS 17TS C13 8.2 C11 1.5_UPDATE.xlsm

Ben

thanks,i already increase Y-cap from 2.2nf to 10nf,ferrite CM choke on the board as picture,the board GND is connected to module GND (module GND is connect with chassiss case).now, I will test module according to your bom,now,thanks

,

i

i

Keep the GND connection as short as possible to minimize parasitic inductances. Here is a link from E2E that the TI team has put together to help design in AEF.

Ben

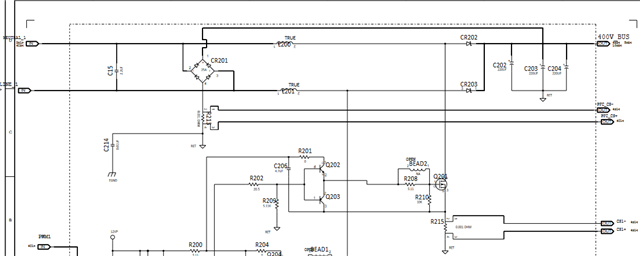

Vinj=12V when AC is connected to grid and module turn on , 1 try to increase CM choke,Y-cap on the regulator side(2.2nf to 10nf),GND of EVM is connected to ground,but Vinj is still 12V on last week,my topology is boost PFC 120kHz +DCDC,PFC as below picture,if TPSF12C1 is not used this topology???

Hi Jin,

hello,I use your parameter,but Vinj=12V when my module turn off ,TPSF12C1 turn on as FIG.2(VDD=12V,module with LISN),Vinj=15V when VDD=15V as FIG.3(with LISN),but Vinj=6V (without LISN ) when VDD=12V,why?

The BOM that I gave causes the TPSF12C1 to go unstable when a LISN is applied to the setup. Try reducing the gain of the TPSF12C1 by changing the Rg resistor from 4.5kohms to 7.5kohms. See quickstart calculator below:

Vinj=12V when AC is connected to grid and module turn on , 1 try to increase CM choke,Y-cap on the regulator side(2.2nf to 10nf),GND of EVM is connected to ground,but Vinj is still 12V on last week,my topology is boost PFC 120kHz +DCDC,PFC as below picture,if TPSF12C1 is not used this topology???

What do you mean when VINJ = 12V? A quick check to see if the INJ pin does not oscillate is to power up the TPSF12C1 but leave everything else turned off.

Ben

hi Ben,Rg=7.5kohms,Vinj =12V as Fig.1 when AC source is not turn on,but it is connected to module.Vinj=6V when AC source is't connected.

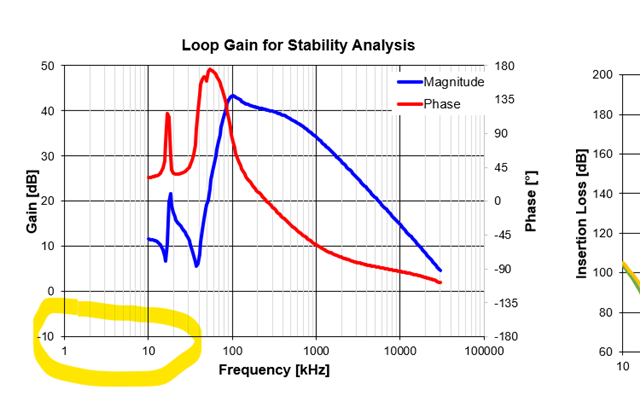

I have a question,is it normal that there don't have phase and magnitude wave at 1-10kHz?

Hi Jin,

The choke data measurement is missing that frequency range. Can you retake your choke data and change the starting point of the frequency sweep to 1kHz?

hi Ben,Rg=7.5kohms,Vinj =12V as Fig.1 when AC source is not turn on,but it is connected to module.Vinj=6V when AC source is't connected.

You can keep increasing Rg to reduce the overall gain of the AEF loop or reduce Rd2 so the impedance to PE GND is lower.

Ben

Increasing Rg will cause the magnitude of the loop gain to not transition so hard as soon in fig.1 between 10-40kHz. In fig 2 the magnitude transition is more subtle between 10-40kHz. It is useful information if you the chokes can be swept from 1K.

Ben

Thanks,I test cm choke parameter from 1k to 30M as below file,I change RG from 7.5k to 12k,VINJ wave as fig.2,it is still saturate when nearby AC current zero crossing,I also change VDD from 12V to 15V,there is no change about VINJ as fig.1

hello, ben, I have two question

1.About CM choke impedance test method, two winding in parallel ,1 is connect to 4,2 is connect to 3 when test cm choke impedance ,as below picture, is it correct? or only need to test 1 and 2,don't need to parallel two winding?

2.Are other engineer use this chip to solve EMI problem in pfc topology that same as my PFC topology?

Hi Jin,

See below:

We have seen many different PFC topologies. We usually recommend the customers to use nanocrystalline chokes because the phase transition of the choke is much softer than ferrite chokes. You can read more about this by clicking on the link below:

Ben

Hi Jin,

If nanocrystalline chokes were used, did you measure the impedance and phase of these chokes and enter the data into the quickstart calculator? The damping network will need to readjusted for nanocrystalline chokes.

Ben

hello, ben, aboutCD2,i don't have 470nF 50v cap, only have 470nf 25V and 330nf 50v ,so i use 330nf 50v cap, but it don't have effect, Vinj is saturate as below picture,I try to change VDD from 12V to 15V, result don't have change,

.

Hi Jin,

Zero-crossings are a problem. My suggestion is to increase the Y-capacitance at the regulator and also increase the choke's inductance to reduce the common mode noise that is getting through the first stage filter.

Ben

Hi Jin,

Yes, others have the zero-crossing problem as well. Others tend to decrease the gain of the AEF loop, increasing the chokes inductance, or adding more Y-capacitors at the regular to reduce the CM noise reaching through the first stage EMI filter.

Ben