Other Parts Discussed in Thread: TPS61022

Hello,

I have encountered an issue with our TPS65987D application in which a spurious reset is observed following receipit of RDO message requesting change from a 15V PDO to 5V PDO.

Configuration as follows:

- TPS65987D operating as DRP acting as SRCto provide power to an Apple iPad. Upon USB-C connection, the iPad selects 15V PDO (SRC via PPHV1) and charges as expected.

- Once the iPad reaches 100% state-of-charge, in some instances, the iPad is observed to send an RDO message requesting switch to the 5V PDO (5V, 0.5A in our applicaion, SRC via PPHV2).

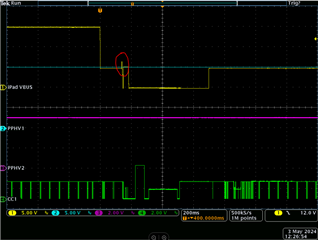

- At this point, it appears that an over-voltage condiciton is detected on VBUS, and the link is reset. Please see attached oscilloscope trace.

This issue appears to be very similar to the issues described in the threads below:

Attached:

- Oscilloscope trace showing VBUS and CC1 traces at point of RDO and subsequent reset.

- Screenshot of LeCroy capture showing RDO message and subsequent reset.

- .pjt file. Please note that this file has had a change made to a non-user confirgrable field made by Conner Gillette, resulting the first thread linked above. Further, please note that the Transmit Source Capabilities, register 0x32, defined in the .pjtt file are overwritten by our own policy manager software at run-time.

I would be gratefu if you could provide any guidance on the above.

Many thanks in advance,