- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hi team,

My customer it trying to use TLV75801PDBVR, but they are facing thermal issue.

Their system has transient heavy load 315mA for 10ms. This will violate the absolute max junction temperature by simply calculating by eq.(8) on the datasheet.

VIN(max)=5.6 V, VOUT=3.3V, max Ta=70C. So the calculated max TJ is:

TJ = ((5.6 - 3.3) * 0.315 ) * 176.9 + 70 = 198.18 C.

So my customer is requesting us to provide transient thermal resistance data to make sure if the device can handle this transient load.

Could you please provide the thermal resistance of TLV75801PDBVR?

Best regards,

Kazuki Ioth

Hi Itoh-san,

Have they already made boards or are they doing a thermal analysis during the design?

We can provide them with an RC network thermal model, which allows them to set a power dissipation vs. time profile and it calculates the junction temperature in time. For this the thermal modeling engineer would need a way to estimate the thermal performance that they can achieve on their board. If they have already made boards, then we can estimate the thermal performance either through a layout analysis or simulation. If they have not made boards then we may be able to make a layout recommendation to achieve a given performance.

Regards,

Nick

Hi Nick-san,

I talked to my cusotmer about this.

Could you share the RC thermal model of the TLV758P with TI's recommended layout?

Best regards,

Kazuki Itoh

Hi Itoh-san,

For this I would recommend using some thermal vias near the GND pin, even though there is not a thermal pad. This will dramatically improve the thermal performance because the thermal metrics reported in the datasheet are simulated assuming no thermal vias for devices that do not have a thermal pad. Besides this recommendation, the general guidelines for improving thermal performance are to have as much same-side and opposite-side copper (i.e. copper on external layers) as feasible.

So with that said, can they estimate the amount of copper near the device on the same-side and opposite-side that they will be able to have, and the number of layers of the board as well as how many of them will be ground planes? All of these factors will change the thermal performance, so having an estimation will be crucial if they want the RC network model to be reliable.

Regards,

Nick

Hi Nick-san,

Okay, please find following board information.

- PCB layout is based on following design

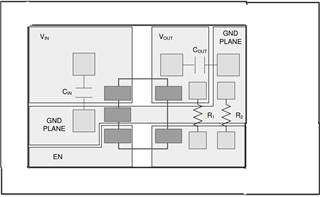

・EXAMPLE BOARD LAYOUT DBV0005A (SOT-23)

・Figure 7-7 DBV Package Layout Example

- Copper thickness:0.043mm (Top layer, including plating) / 0.035mm (internal GND layer)

- Layer count: 4 (Internal layers are all GND layers.)

- Copper area: ~60mm x ~60mm

- Misc :3 thermal vias are located near GND pin.

Best regards,

Kazuki Itoh

Hi Itoh,

Can we assume that the 60mm x 60mm copper is on both the top side and bottom side or just one of them (e.g. just bottom, and the top is as Figure 7-7)? I think everything else is clear.

Regards,

Nick

Hi Nick-san,

60mm x 60mm copper is on both the top side and bottom side.

Best regards,

Kazuki Itoh

Hi Kazuki-san,

Nick is out of the office today and he will get back to you when he returns to the office tomorrow.

Thanks,

Stephen

Hi Itoh-san,

Got it. I'll get a request submitted to create the thermal model.

Regards,

Nick

Hi Itoh-san,

I also need the board size. Do they have an estimate of the board? Or is the 60mm x 60mm the full board size?

How should we assume that the top layer ground copper is laid out? Should it surround the recommended footprint as below?

Regards,

Nick

Hi Nick-san,

The board size is 90mm x 75mm FR4 PCB. PCB thick ness is 1.2mm.

The customer's PCB layout is basically following the datasheet recommendation (Figure 7-7).

Best regards,

Kazuki Itoh

Hi Itoh-san,

Thank you for the board dimensions. I understand that they will use the recommended board layout, but my question is in regards to the 60mm x 60mm copper on the top layer because the recommended layout has copper for VIN, VOUT, etc. So the question is this: how do they want the 60mm x 60mm copper to be laid out for simulation purposes? Should we have the thermal modeling engineer surround the recommended footprint to expand the GND copper to 60mm x 60mm?

Thanks,

Nick

Hi Nick-san,

My customer want us to simulate the 2 layouts below:

1. 60mm x 60mm copper surround the recommended footprint to expand the GND copper to 60mm x 60mm as you prposed

2. The layout without expanded GND copper and copper on bottom layer for the reference (They want to make sure the effect of the copper on the transient thermal performance)

Also, the customer's load condition has changed. The worst case is 210mA load for 20ms.

Best regards,

Kazuki Itoh

Hi Itoh-san,

Okay got it. I think everything is clear now and I got the request submitted. I think the thermal modeling team has been a bit backed up lately, and requests have been completed in approximately 3~4 weeks. I'll update you when I hear back.

Regards,

Nick

Hi Itoh-san,

I just checked and there has been no update on the model request. It's possible that they are backed up. I sent the modeling engineer a message about it. Sorry for the inconvenience.

Regards,

Nick

Hi Nick-san,

OK. Could you let me know the estimated schedule?

Best regards,

Kazuki Itoh

Hi Itoh-san,

I reached out to our thermal modeling engineer again for an estimated timeline. He is out of office this week and returns next week, so I hope to hear back from him then.

Regards,

Nick

Hi Itoh-san,

The thermal modeling engineer finished the models this morning, see attached. There are instructions on how to use the model on the Thermal Model-Die Temp tab. Please let me know if you have any questions.

5DBV_20878_TLV75801P_Baseline_PCB_RC_Network.xlsx

5DBV_20878_TLV75801P_Extended_GND_PCB_RC_Network.xlsx

Regards,

Nick