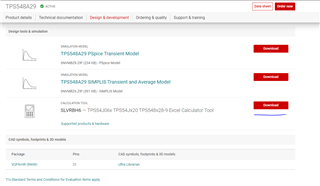

Tool/software:

Hello, We have been having issues with our boards and the DC Reg (TPS548A29RWWR) shorting to ground through Vin/SW.

- Input is 11-14V; Output is 5.1V, 10A max (initial thought was we needed 7-10A, but we now only need 2A so this could be changed)

- Our goal was efficiency over size, so design uses 600kHz sw frequency.

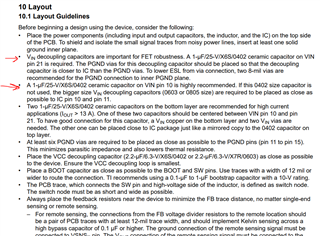

Reading through the forum here, we found that the common issues for this series was either layout or transient voltage spikes. We checked our layout, and added Elect-Alum caps to the input to help dampen anything that might be sneaking through, as well as increased the output capacitance. Further up the line, there is a TVS diode with a max clamp of 24.4V (SMCJ15A) on the input. We based these choices on the EVM schematics.

Reading the datasheet deeper I believe I read the VCC capacitance (section 7.3.1) as "at least 2.2uF" instead of correctly "at least 6V rating" on the VCC pin. Down below in the design example though (section 8.2.2.9) it says minimum of 2.2uF. Any issues here?

- 1st iteration was more stable, in that it would pass all tests in the lab but has been failing in the field.

- It seems that our 2nd iteration is less stable than the first, and fails much easier even in the lab.

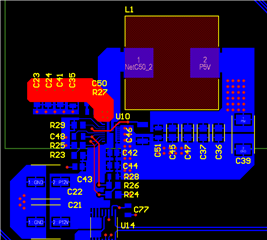

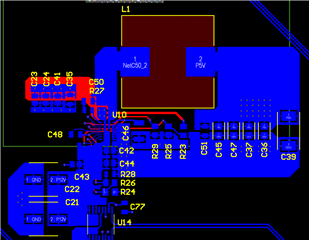

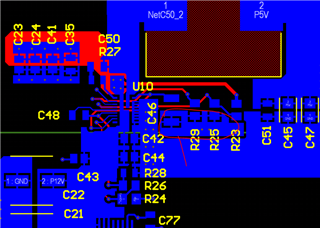

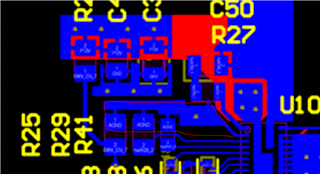

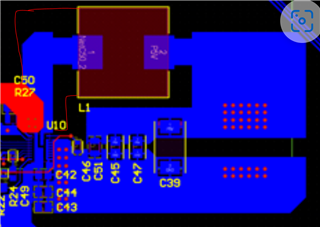

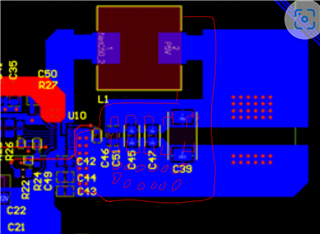

Sch_Initial_Design_TPS548A29_5Vout.png