Other Parts Discussed in Thread: TPSI3052,

Tool/software:

Hello team,

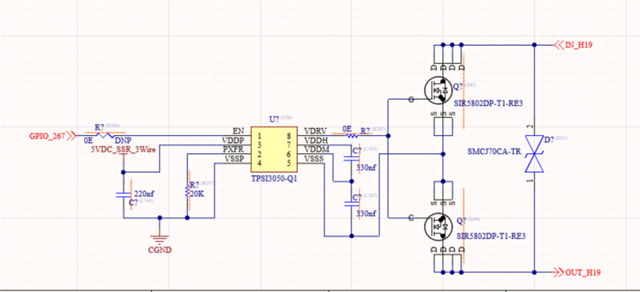

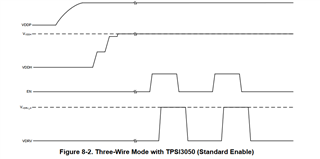

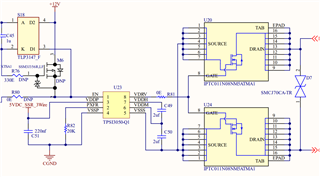

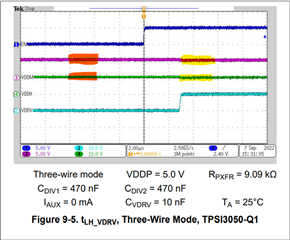

I have some doubt w.r.t the measurement of each node (EN, VDDP, VDDH, VDRV) of TPSI3050. Also, I would like to take measurements and plot a graph as mentioned in your datasheet (Refer below attached image)

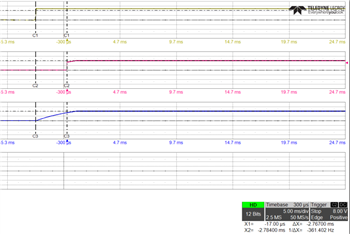

FYI, we have 4 channel DSO and I have measured the primary side voltage EN w.r.t GND.

But how to measure the secondary side voltage VDRV and VDDH ?

Looking for your response.