Other Parts Discussed in Thread: UCC28951, UCC28950, UCC28950EVM-442

Tool/software:

Hello Team,

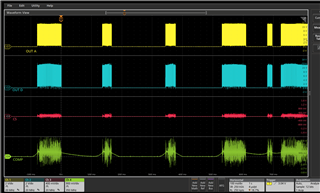

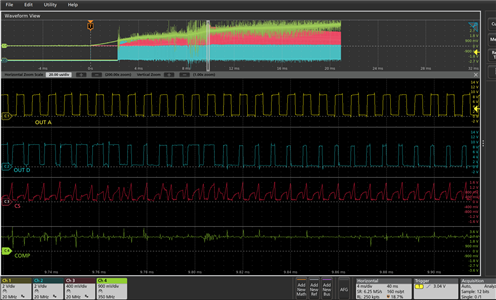

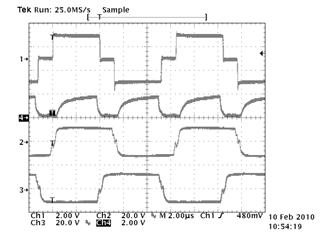

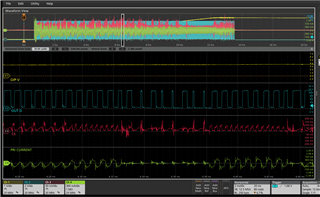

As shown below gate pulses observed in our power converter during startup with no load condition. We operating in peak current mode control, Could you clarify on CH-3 & Ch-4 PWM output nature?

In PSFB , we should get 50% fixed duty at primary side right. Could you help us out?

CH1- QA gate , CH2-QB gate , CH3 - QC gate & CH4 - QD gate.