Tool/software:

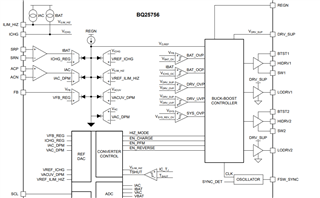

Hello, I am testing with the BQ25756E evaluation board at the moment and have only changed the Richg resistor to 2.44k to produce a charge current close to 17A, all other components are stock. I checked beforehand and the stock mosfets and inductor seem to be able to handle the increased current. My testing scheme consists of the power supply, the charger board, and the battery. My Vchg=29.4V, Ichg=17A, Fsw=250kHz.

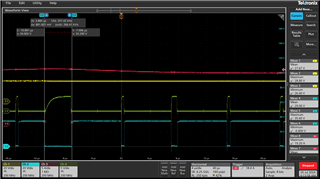

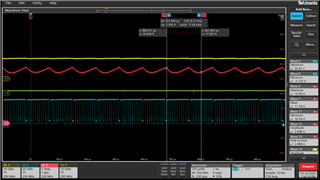

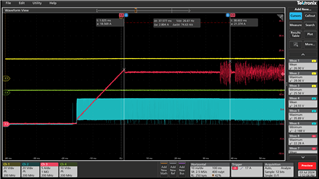

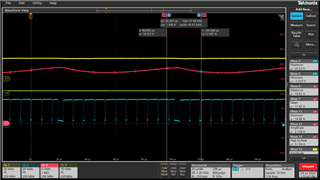

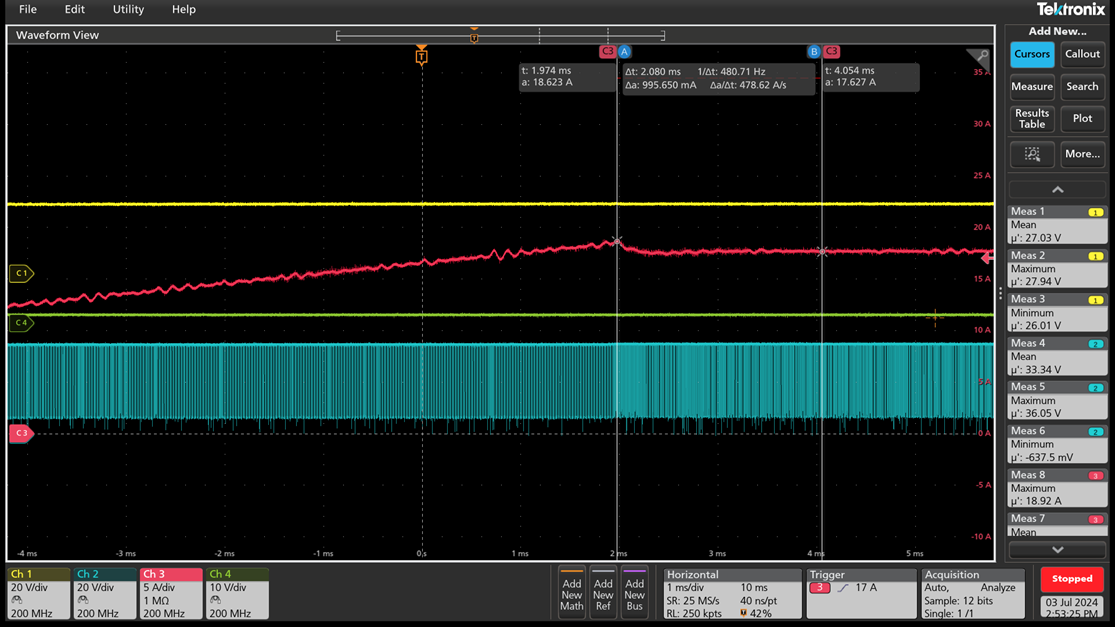

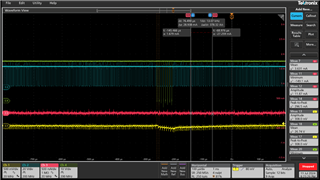

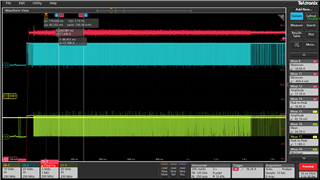

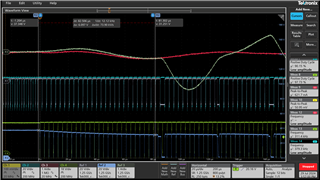

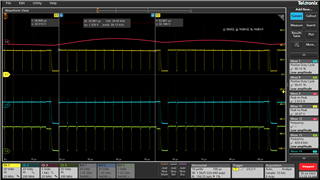

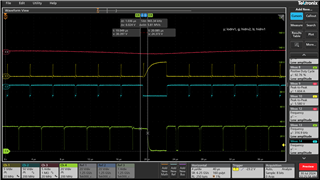

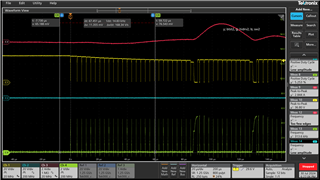

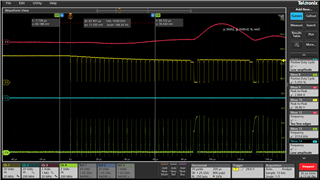

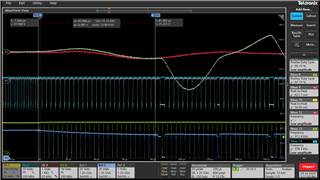

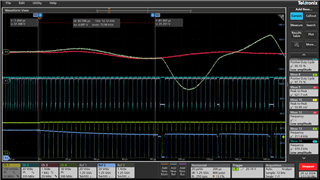

Red: Ichg, Yellow=Vout, Green: LODRV1. Blue: HIDRV1.

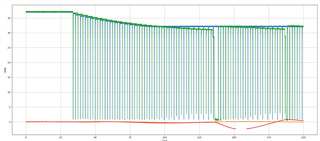

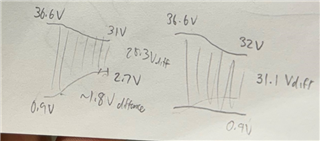

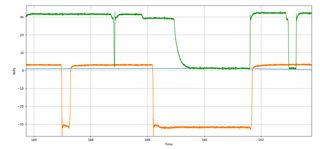

My battery voltage is 27V, so I am expecting a full charge current of 17A at turn on. When I turn on any of the three while the other two are on, in a minority of cases I see a normal turn on where Ichg=17A, Fsw=250kHz, and Iripple=~2A. However, most of the time I am seeing an oscillating turn on where Fsw=~133kHz aka 1/2 of programmed value, and Iripple=~5-7A, which causes my Iout to be ~17.9A at steady state. This oscillating behavior exists for 0-2minutes before eventually it returns to normal Iripple.

What could be causing this, and is there any way to fix this? Any help is appreciated.

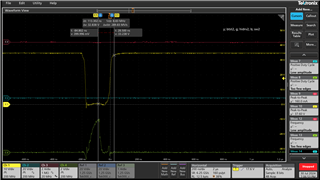

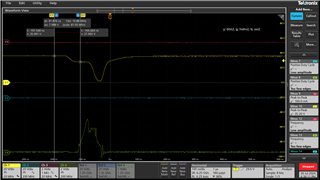

I will include waveforms of the steady state, gate drives, and transients below.

I've noticed that at a normal turn on event, Fsw=~133kHz during the current ramp up, before evening out to ~250kHz when Iout begins to be regulated is this intended? If this is intended, does the charger think it is in ramp up mode still? None of these behaviors occur with Eload testing, only battery load.