I have used the Switcher Pro program to design 5 power supplies. A 12V 6A based on the TPS40054 and 5V, 3V3, 1V9, 1V2 based on the TPS54620.

The TPS54620's are fed by the 12V supply, so lets start with the 12V supply first (Switcher Pro report:4721.12V.pdf SCH: 7462.supplies.pdf PCB:4405.supplies_pcb(top+mid1).pdf 0844.supplies_pcb(mid2+mid3).pdf 1273.supplies_pcb(bottom).pdf).

The 12V supply was designed with a f_sw of 200khz, but as I want to synchronize the supplies I use an external oscillator to provide 200khz and changed Rt to 330k to get a free running freq of 161kHz so that 200kHz falls in the 20-30% higher range as stated as necessary in the datasheet. C_ss has been increased to 68nF to ramp somewhat slower.

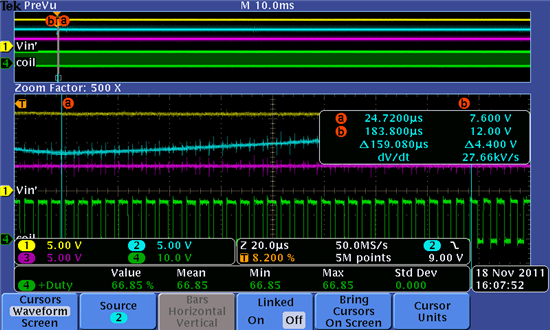

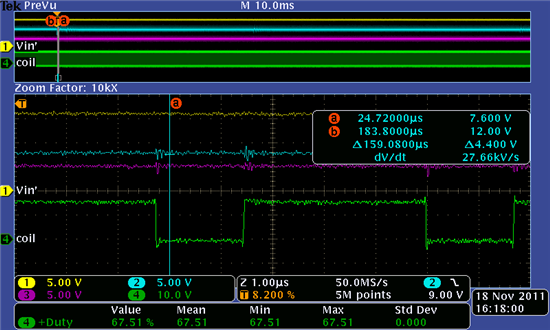

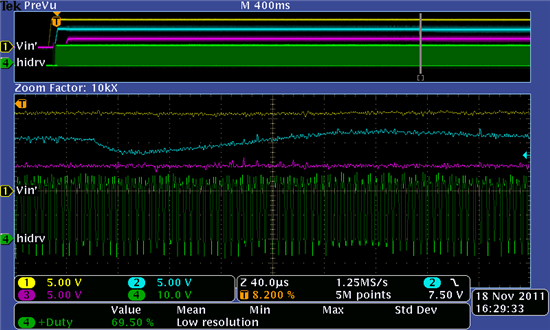

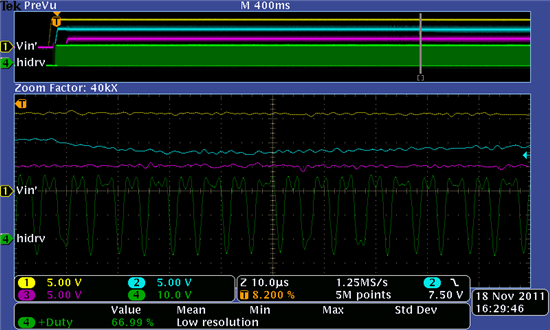

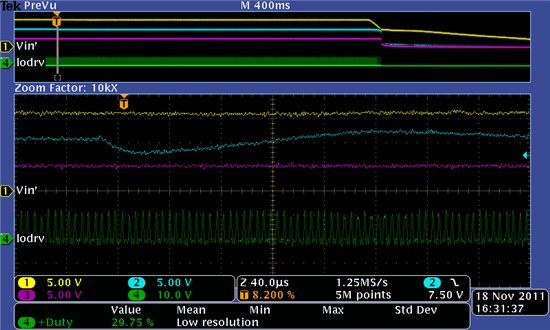

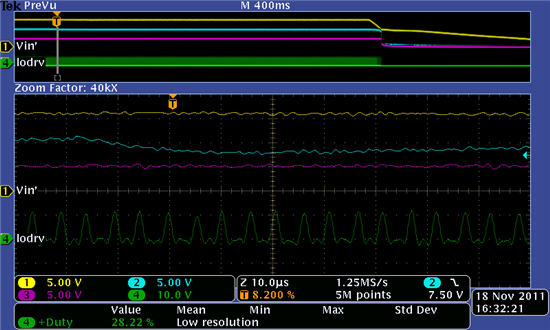

Observations so far on 12V supply:

- The frequency of the sync signal was initially to low (~170khz), the device however starts providing 12V if the input voltage is just above the UVLO of 14.4V. If I increase the input voltage the output voltage drops to 6-8V. If I add load (1.5A) the voltage dips to 11.6V at the output of the coil.

- If I increase the sync frequency to 200 kHz I have to decrease the value of Rkff, or the device does not seem to start. I also have to connect additional load (the circuit itself provides very little load until the 12V is within limits), the voltage on the output is only 9.7V (Vin=16V) to 9.9V (Vin=24V).

Efficiency is important in this application as the board is battery powered (18-36V). Therefore I have (hopefully correct) chosen a low switching frequency and large coil.

Any pointers on where to start debugging?