Tool/software:

Hi all,

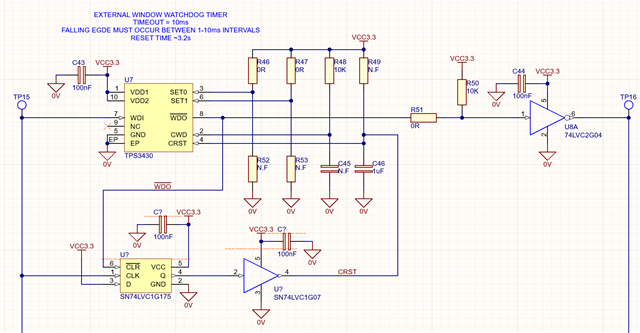

Im testing a prototype PCB we have developed and we are using the TPS3430 as part of the circuitry. We send a pulse to the WDI input inside of a 1-10ms window to keep the output enable of a level shifter enabled.

If the pulse arrives too late or too early the output enable is de-asserted to indicate a fault. When we intentionally disable the WDI input pulse to test it works fine however the reset delay kicks in and we get a momentary output of the TPS3430 which is undesireable?

The reset delay is set to around 3.2s (1uF capacitor on CRST) and it gives a ~3.2s delay when the WDI pulses resume (which we like!).

Ive noticed the app notes to latch the WDO output when de-asserted which looks good but wondered if there was an all in one solution, before I go ahead and look at adding the latching circuit (probably with the D flipflop portion added so the micro can reset it without a power down).

Cheers all.