Other Parts Discussed in Thread: UCC27511

Tool/software:

Hi,

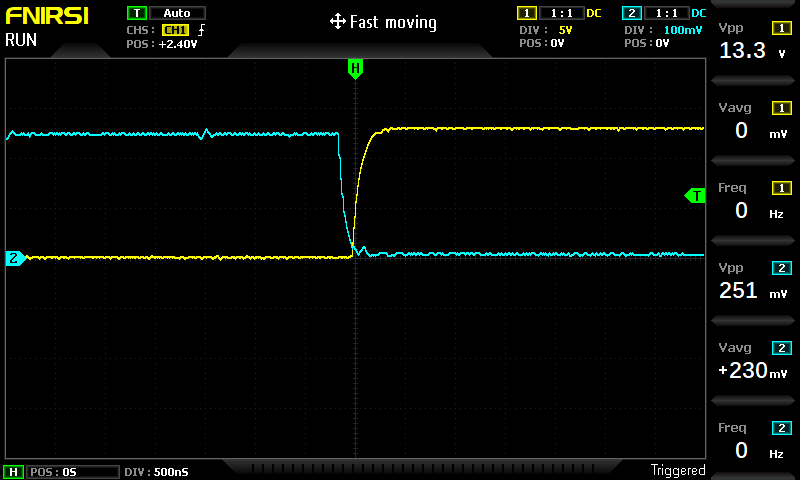

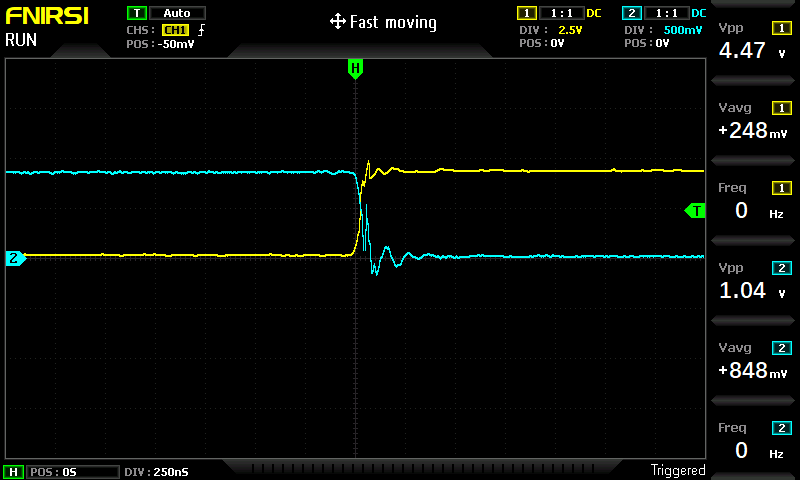

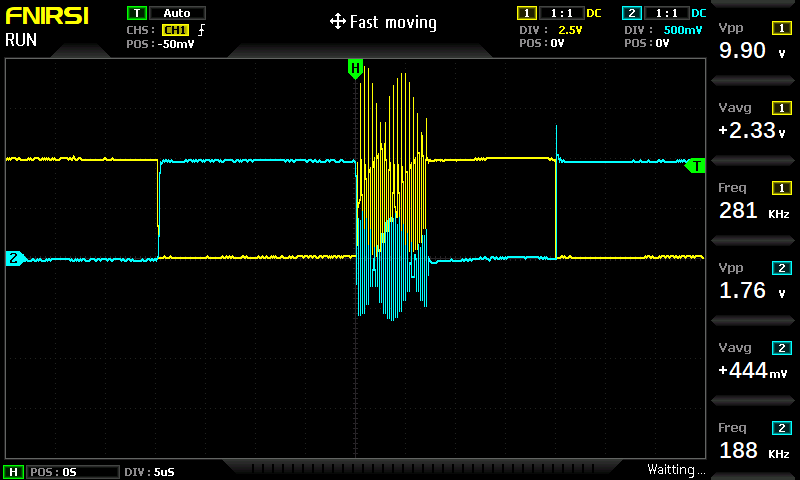

I am continuing a thread: Half bridge circuit with UCC21550 not working with Will as this thread has been locked due to inactivity for more than 30 days.

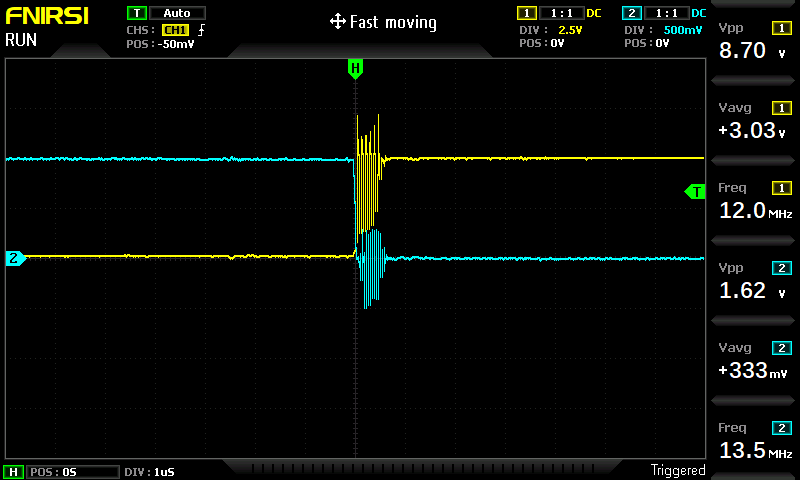

I have increased the dead time to 443ns (R_DT 50K) but the issue is not resolved.

What else could be going on there?

Kind regards,

Bright