Other Parts Discussed in Thread: PMP40580, TL431

Tool/software:

The previous thread was locked, so I couldn't add to it, but I did realize my error with only trying to power the LLC. I didn't think I could startup the chip with an external supply to the VDD pin - I thought it had to be charged internally through the HV pin, so that answer was helpful.

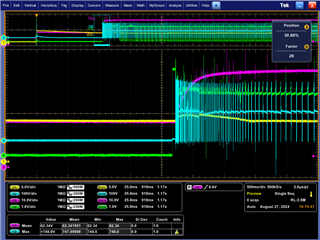

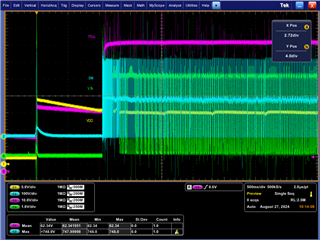

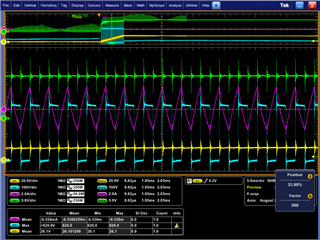

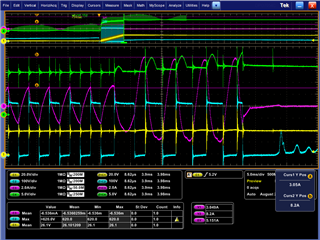

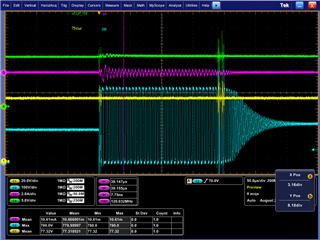

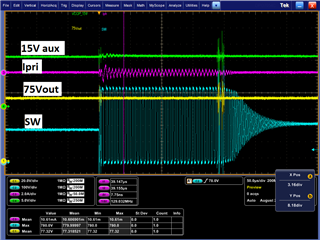

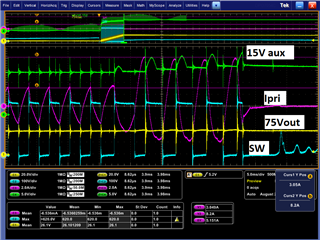

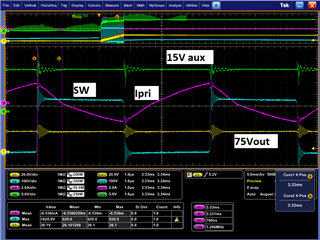

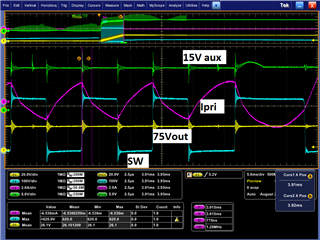

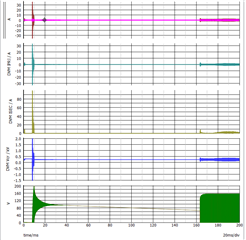

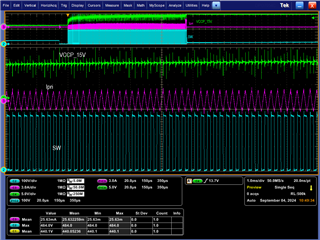

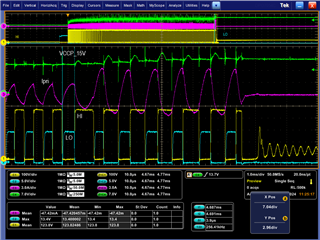

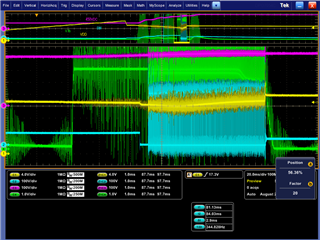

However, I'm now running into what is probably a fault on startup. I've attached a couple scope plots, my schematic, the transformer datasheet I'm using, my excel design sheet, as well as the simplis model of my design for reference. The good thing, I think, is that the simplis model mimics my measurements on the bench, but I'm not entirely sure where to start looking for problems. My biggest concern is whether I've modeled the transformer properly, but I think all of the values in my design match what I get from the design spreadsheet. The scope plots show the 450V input, the VDD pin, the FB pin, and the switching node SW.

General specs of the LLC design -

Vin is 450VDC; Vout is 75VDC; Iout max is 2.667A.

The UCC256404 starts switch, and then stops after about 5ms, which is what the sim does, too, though the sim does restart after another 30ms or so, and my PCB does not. I attribute that to certain fault modes not being implemented. The output of the LLC (not shown in the scope plot) should regulate to 75V, but it gets to only about 40-45V before something shuts it down, also the same as the sim.

I'd appreciate a look over my design sheet and/or schematic to see if I've done anything incorrectly, or some thoughts on where to look for issues. I'm new to both LLC designs and SIMPLIS, so I definitely have a learning curve I'm navigating.

Thanks,

Joe

UCC25640x Design Calculator Rev4 take2.xlsx

LLC Transformer.pdf3630.n10812F-0_Schematic_Aug5_2024.pdfUCC25640x Simulation Test Bench ERGdesign.zip