Tool/software:

Hi TI experts,

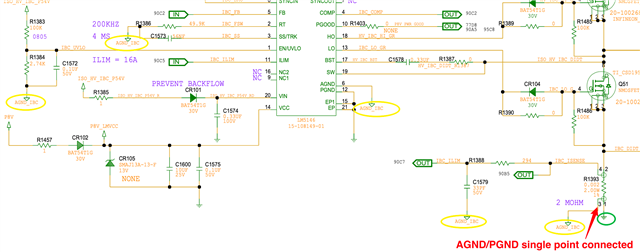

I use LM5146 to convert 54V to 8V/13A, the Fsw was set to 200kHz by connecting 49.9Kohm to RT pin.

Observed one pulse in every two is missing and duty cycle is incorrect.

Can you help look into this issue?

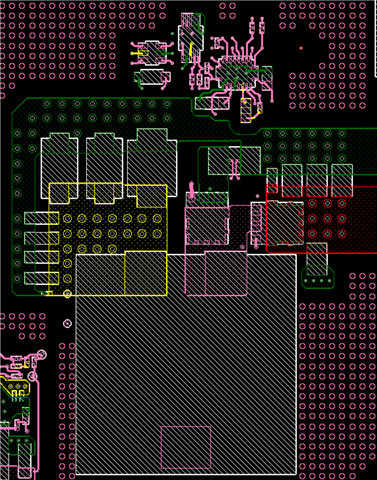

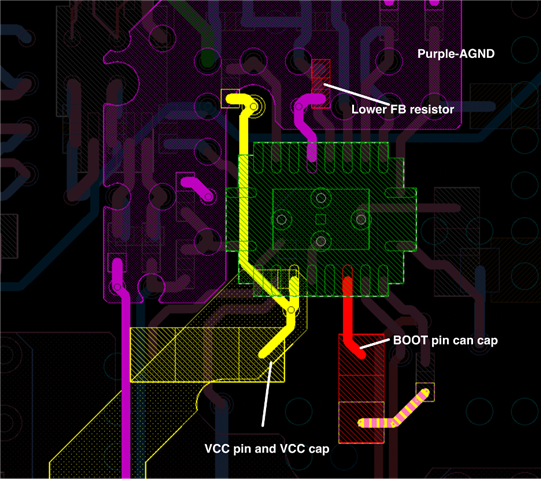

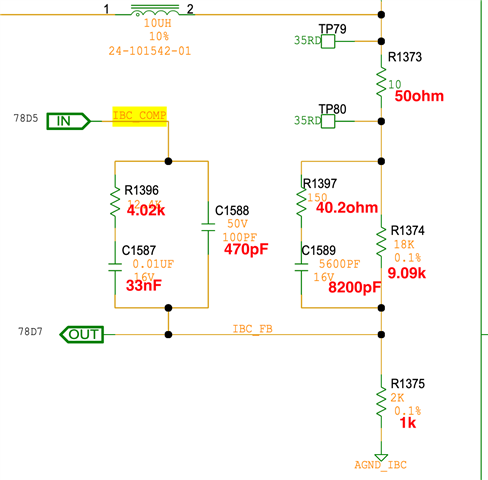

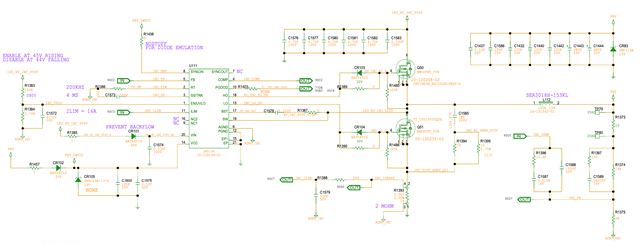

Schematic:

Yellow- Vout, Blue- Switching node

Yellow- Vout, Blue- Switching node, zoom in

Thanks

Neo