Other Parts Discussed in Thread: MSP430F5529, TPS92633-Q1

Tool/software:

Greetings,

Can we connect 2 ICs of 6 PWM pins parallelly connect to a single GPIO pin of MSP430F5529?

will it work as expected ?

Best regards,

Tex

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Greetings,

Can we connect 2 ICs of 6 PWM pins parallelly connect to a single GPIO pin of MSP430F5529?

will it work as expected ?

Best regards,

Tex

Hi Tex,

Yes, you may connect multiple PWM pins in parallel to control dimming from a single GPIO pin.

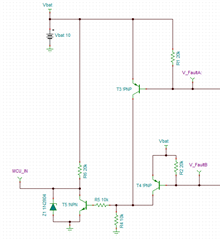

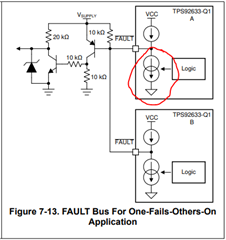

I recall in your previous query you wanted to connect these 2 ICs in the "One-Fails-Others-On" FAULT Bus configuration. If so, please note there is an error in Figure 7-13 of the TPS92633-Q1 datasheet. In order to configure the devices in One-Fails-Others-On mode you will need to connect a separate PNP transistor and pull-up resistor to each fault pin, as shown in the schematic below.

I've attached the full TINA-TI simulation file for your reference.

Best of luck with your continued design.

Regards,

Zach

Hi Tex,

The schematic is figure 7-13 is actually correct.

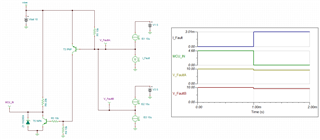

I made an error in my model by using a pure open-drain configuration instead of a 3mA pulldown current. See updated model below.

The schematic I recommended in my last post will also work, however it is not necessary to include the additional components.

My apologies for the confusion.

Best,

Zach

Hi Zach,

Apologies for delay in response,

Please clarify few queries related to FAULT PIN

The schematic is figure 7-13 is actually correct.

So, I can implement that circuit as it is ?

1. Could you please explain how circuit mentioned in figure 7-13 works ?

2. In figure 7-13 They used 2 IC to that single circuit, Can i use 4 ICs to that single circuit ?

3. Why MCU is connected in your previous circuit ?

4. So, as per your previous circuit this pin will also connected to MCU as input?

5. Will that circuit works without controller ?

6. Could you please mention Part numbers & resistor tolerance of those components and If you have any design/Schematic file implemented this circuit with the TPS92633-Q1 please share..

Kind regards,

Tex

Hi Tex,

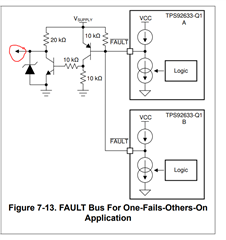

1. Could you please explain how circuit mentioned in figure 7-13 works ?

The Fault pin is connected to an internal 3mA pulldown current sink. During a fault, ~3mA is pulled through the base of the PNP which turns on the transistor and pulls the collector high. When the collector of the PNP is high, the NPN transistor also turns on and toggles the voltage at the MCU input, indicating that a fault has occurred. The 0.7V emitter-to-base voltage drop across the PNP keeps the shared fault bus high which allows the other devices to remain on when one device experiences a fault. This is the one-fails-others-on application.

2. In figure 7-13 They used 2 IC to that single circuit, Can i use 4 ICs to that single circuit ?

Yes, you can use 4 ICs with the shared fault bus.

3. Why MCU is connected in your previous circuit ?

To read back when a failure occurs.

4. So, as per your previous circuit this pin will also connected to MCU as input?

If you want to use your MCU to read back when a failure occurs, this pin will be connected to MCU input. This is the typical application.

5. Will that circuit without controller ?

For the one-fails-others-on function, the MCU is used to monitor if a fault occurred.

6. Could you please mention Part numbers & resistor tolerance of those components and If you have any design/Schematic file implemented this circuit with the TPS92633-Q1 please share..

Select transistors with max Vce voltage that is greater than your battery voltage. 1% resistors.

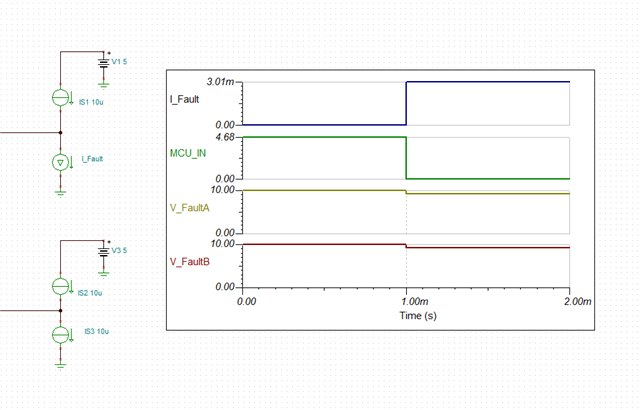

Here is my updated TINA-TI simulation file.

Regards,

Zach

Thank you so much for your valuable reply zach!,

i have been reviewing the simulation which you have sent..

Here,

I have less knowledge in LTspice.So, I request you to explain few things.

1. Why current generator is used under fault condition ?

2. Why voltage is reduced in both the ICs while the fault is only in 1 IC ?

Kind regards,

Tex

Hi Tex,

1. Why current generator is used under fault condition ?

The current generator is used to simulate the 3mA internal pulldown of the TPS92633-Q1 fault pin. This is a more accurate model than my previous open-drain configuration. Notice figure 7-13 shows an internal current sink connected to the fault logic.

2. Why voltage is reduced in both the ICs while the fault is only in 1 IC ?

The voltage is reduced by the 0.7V emitter-to-base voltage drop across the PNP. This voltage drop occurs at both fault pins because they are connected together directly. Even though there is a small voltage drop, the fault bus remains logic high which allows the other device to remain active (one-fails-others-on).

This is a simple but elegant solution that relies on the internal current sink and the fact that the PNP is a current-controlled device.

I hope this helps.

Regards,

Zach