- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hi, Team!

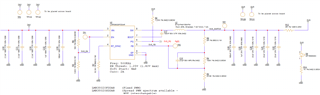

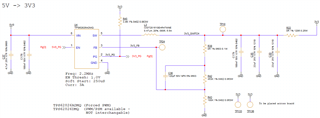

We have two TI chips: LMR38020FDDAR and TPS62826ADMQ connected together on 2 of our designs in the following way:

So, the 5V coming from the LMR38020FDDAR is connected into the Vin of the TPS62826ADMQ, and PG of the LMR38020FDDAR is connected into the EN of the TPS62826ADMQ through a pull-up resistor.

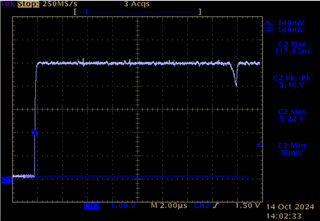

We have observed a dip occurring on the EN line of the TPS62826ADMQ on both the designs. The capture is provided below:

After rigorous investigation of the potential cause of this, we could not find an issue with our design, so we have ordered two evaluation boards: TPS62826AEVM-126 and LMR38020EVM.

We have connected them together without changing any components populated on the boards. We have connected the Vout of the LMR38020EVM into the Vin of the TPS62826AEVM-126. We have also connected the PG line of the LMR38020EVM into the EN of the TPS62826AEVM-126. They powered up alright, however when we scoped the EN line, we observed the same behaviour : the dip of 2.2V, 14us after the rise of the line:

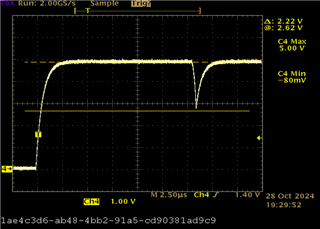

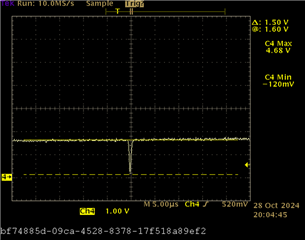

We have then tested just TPS62826AEVM-126 in isolation. We have powered it with 5V and pulled the EN line up to VIN with the 27.8k ( same as the LMR38020EVM PG pull-up) . And saw the dip on the ramp up of the EN line:

So, we think the dip is caused by the TPS62826ADMQ chip.

Any suggestions why this is happening?

Since we see this happening on the evaluation boards we know this is not to do with our particular design, but would like to know the reason why this is happening and how we could use the chips such that we minimise this problem.

Thank you very much for your help!

Best wishes,

Kristina.

Hello Kristina,

thanks for reaching out in E2E and for providing this detailed explanation of your analysis.

Have you checked if the VIN of the TPS62826A is also showing this dip? I would assume that VIN can drop once the TPS62826A starts operating, which would then reflect o the EN signal via the pull-up resistor. In this case you could try to increase the input capacitor TPS62826A.

Please let me know your feedback.

Best regards,

Andreas.

Kristina,

with the additional information from the other thread (https://e2e.ti.com/support/power-management-group/power-management/f/power-management-forum/1425279/lmr38020-lmr38020fddar---dip-on-the-pg-line-14us-after-the-rise-of-the-line) it seems that you already have checked the 5V rail and did not observe any dip.

I just found out that this dip is a known behavior of the TPS62826 device due to some internally activated pull-down pulse during start-up. It will not affect the device operation. This dip can be eliminated by connecting EN to VIN directly or in your case reduce the value of the pull-up resistor to minimize the dip.

In addition I want to mention that the LMR38020 can deliver 2A output current. The TPS62826A is a 3A device. I would expected that the average input current of the TPS62826A is lower due to the switching duty cycle and probably it would fit to the 2A capability of the LMR38020. But in some peak conditions the TPS62826A could draw a higher current from the LMR38020. So I would suggest to check for current peaks at the input of the TPS62826A under worst case load step or during startup and make sure the 5V supply is stable all the time.

Best regards,

Andreas.

Hi, Andreas!

Thank you very much for your reply!

We have checked for current spikes before, and found that 5V is stable at all times.

Could you please clarify, when you say " dip is a known behaviour of the TPS62826 device due to some internally activated pull-down pulse during start-up", is this written somewhere in the datasheet or where could I find this information?

Thank you,

Best wishes,

Kristina.

Hi Kristina,

that is what I also thought. I will reach out and see if this information can be added to the datasheet.

Thanks for your feedback and best regards,

Andreas.

Hi, Andreas

Thanks for your reply.

Could you please confirm does this internal pull-down behaviour only occurs on startup or are there other situations where this EN blip might occur?

Also, could you please advise if there is a pin compatible equivalent part which does not do this?

Thank you!

Best wishes,

Kristina.

Hello Kristina,

the internal pull-down behavior only occurs once during startup. I'm not aware of any other scenario with such a dip on EN.

As said before, the dip is not affecting the device functionality and could be ignored.

There would be an older pin to pin compatible device, which is the TLV62595. But this has no forced PWM option, it is automatically transitioning to PSM (discontinuous conduction) under light load conditions. Let me know if you are still interested.

Best regards,

Andreas.

Hi,

There was no feedback since a while, so I assume this tread is resolved and can be closed. You can still reply to this thread after it is closed, or you can create a new thread.

Best Regards,

Andreas.