Other Parts Discussed in Thread: UCC28180, UCC24624, UCC25600,

Tool/software:

HI ALL

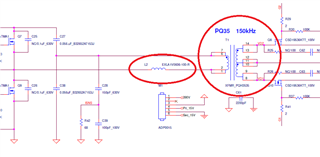

We are currently designing a 1000W AC/DC system using a PFC UCC28180 + LLC UCC256604 without HV startup + SR UCC24624 configuration.

The design specification for Vout is 40V/25A.

We have identified an issue where, under loads exceeding 320W, the temperature of the Primary-Side MOS increases abnormally fast. Within approximately one minute, its surface temperature can reach 100°C.

If this condition persists for a period of time, the temperature can exceed 180°C, resulting in burnout.

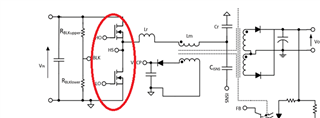

I suspect that it might be caused by a shoot-through short circuit in the half-bridge circuit, but I am unsure how to address it.

1.Replace with a faster FRFET MOSFET? Which parameters should we focus on? Ciss, Coss, or td(on), td(off)?

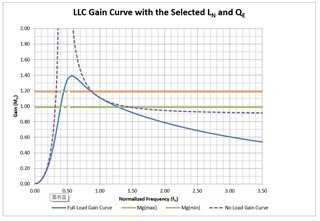

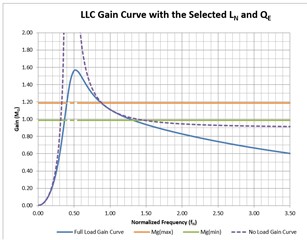

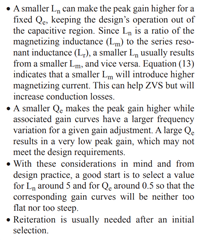

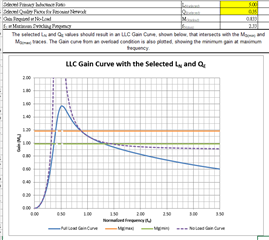

2.Modify the design to make the LLC Gain Curve flatter (with a higher QE value?ZCS?ZVS?).Attach the design table.UCC25660x_Design_Calculator_Rev1.8_Noah.xlsx

3.Under the existing design architecture (without modifying the transformer), adjusting Ln and QE while keeping the LM value fixed means only the LR value can be adjusted. Can the LR value be equivalently represented as LLK (leakage inductance) + LR (external inductance)? I am unsure if my interpretation is correct.

EX: LP=L2+ LLK (leakage inductance) = 10 + 12= 22 uH .Attached is the circuit diagram.sch_adp1000a_e20_20241118.pdf

Thanks

Regards