Tool/software:

- Output power = 25kVA.

- Output Inductor =196uH.

- Output Voltage = 220-240V (Phase to neutral).

- Switching frequency: 45kHZ.

- DC-BUS VOLTAGE = 830V.

- VDD-COM = 15V.

- VEE-COM = -4V.

- VCC-GND = 5V.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hi Rodrigo,

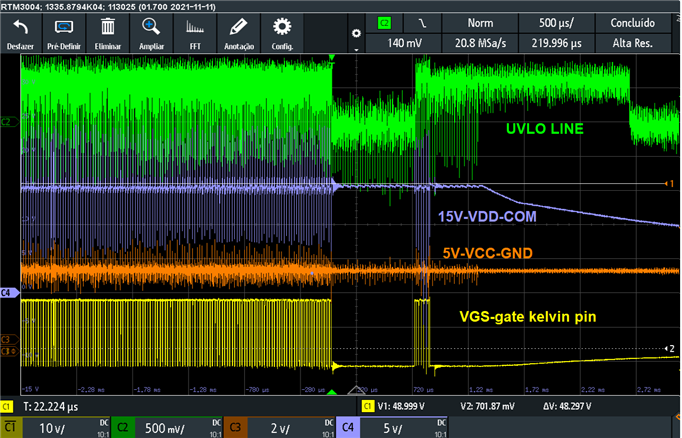

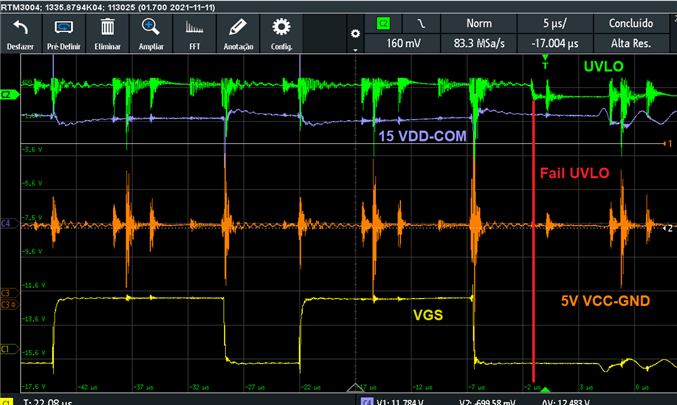

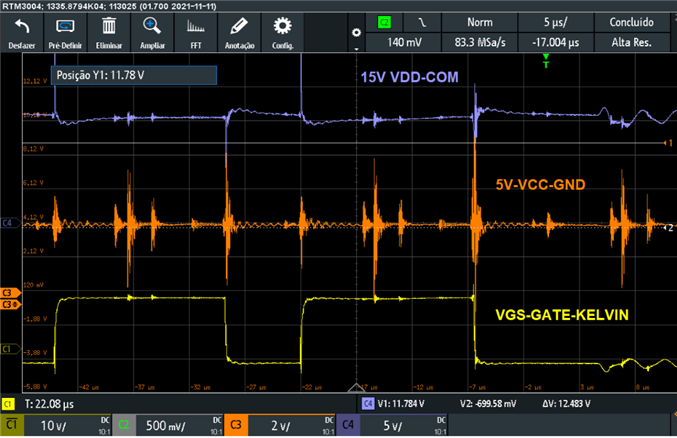

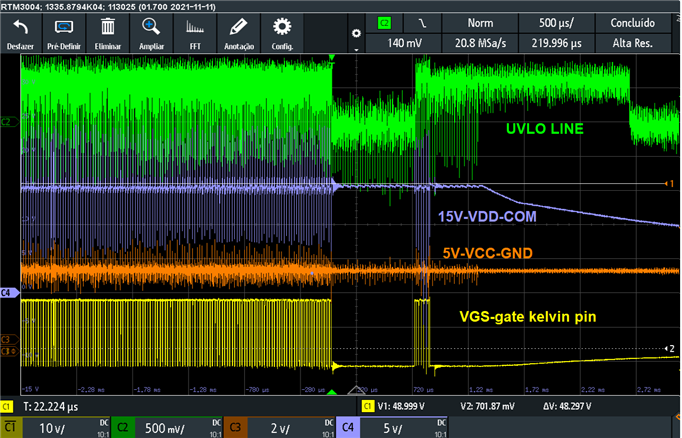

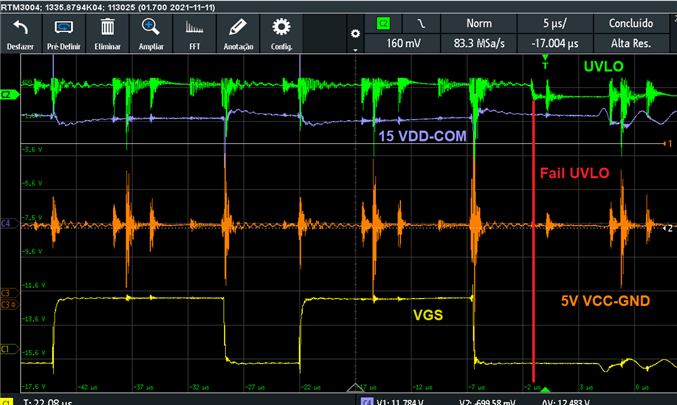

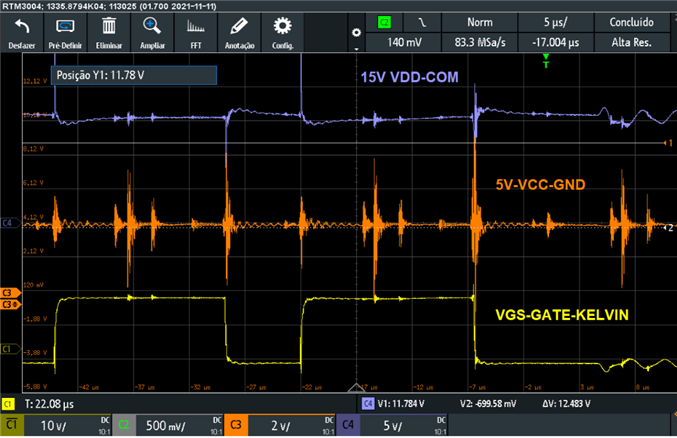

Thanks for the above waveforms. The waveforms look extremely noisy, and I wonder if it's caused by system noise coupled into the probe, or the actual waveforms seen on the pins. Can you confirm the probing method and type of probes used?

If they are the actual voltages seen on the pins, then I can see clear violations of our specs above the absolute maximum values. For example VCC seems to drop to ~-4V and overshooting to ~10V. I definitely won't say the VCC and VDD waveforms look fine.

Also, two observations I have on the waveforms/your description:

If you can, I would suggest capturing the VCC/VDD waveforms as close to the pin as possible, using a probe with small ground loop. Thus we can have a clearer picture on whether UVLO triggered. Also, does this issue happen only on one board, or on multiple boards you're testing?

Looking forward to your reply,

Vivian