Tool/software:

Hi TI Team,

When we perform the USB3.0 LFPS testing, we failed at LFPS Vtx-DIFF-PP and LFPS TBurst testing ,do you have some suggestion about this?

Should we modify which parameter to fix this issue?

Thanks!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hi TI Team,

When we perform the USB3.0 LFPS testing, we failed at LFPS Vtx-DIFF-PP and LFPS TBurst testing ,do you have some suggestion about this?

Should we modify which parameter to fix this issue?

Thanks!

Hi,

It seems that your LFPS signal swing is too high for the test to pass. The TUSB544 will pass through LFPS from your USB host, but should not significantly impact the signal swing. Can you lower the LFPS swing coming from the USB host?

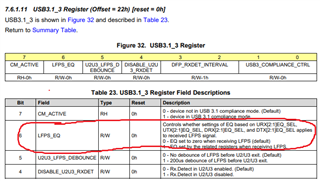

If you are using I2C mode on the TUSB544, I recommend checking that the LFPS_EQ register is set to '0'. This would disable any EQ gain on the LFPS signal.

Best,

Shane

Hi Shane,

We use GPIO mode on the TUSB544,could you please help to confirm how to disable the EQ gain on the LFPS signal?

Thanks!

Hi,

If you're in GPIO mode LFPS EQ gain should be disabled by default. You'll likely need to lower the LFPS swing coming from the USB host.

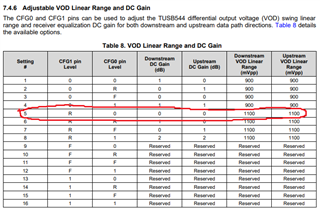

You can try using setting 'R0' on the CFG pins to eliminate DC gain from the TUSB544. This may help lower the voltage swing, however the USB host is the primary means to change LFPS voltage swing.

Best,

Shane

Hi Shane,

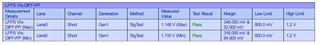

Below is the LFPS test result of Host, it can pass the LFPS test, should the Host change the LFPS swing voltage to which level?900mV?

Hi Shane,

If we set 'R0' on the CFG pins to eliminate DC gain from the TUSB544,will it affect the TX Eye diagram performance?

Thanks!

Hi,

1. Yes 900mV would be good to try for the host LFPS swing. It seems like the host passes but the swing is close to the high limit.

2. Setting 'R0' to eliminate DC gain can lower the USB signal swing, however the Eye diagram should not be significantly impacted.

Best,

Shane

Hi Shane,

TUSB544 compliance report1:

CFG pin:"FR" for TUSB544

Set up:Host+2000mm Cable+TUSB544

TUSB544 ComplianceTest Report1.docx

TUSB544 compliance report2

CFG pin:"R1" for TUSB544(1)

CFG pin:"FR" for TUSB544(2)

Set up:Host+2400mm Cable+TUSB544(1)+1850mm Cable+TUSB544(2)

7317.TUSB544 ComplianceTest Report2.docx

Thanks!

Hi,

It seems like you've got some margin in the compliance report, so it may be ok to reduce your DC gain. To do this, use CFG setting 'R0' on the TUSB544:

If the LFPS swing is still too high after setting CFG to 'R0', you need to turn down the LFPS swing on the USB host.

Best,

Shane

Yes CFG will affect both DP and USB performance. In general, its best to have the highest linearity range (1100mVpp) for both USB and DP.

DC gain will slightly impact the signal swing for both USB and DP.

Best,

Shane