Tool/software:

Hi,

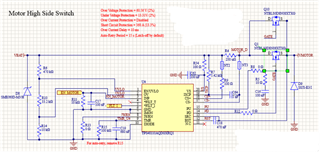

We are using the TPS48110 high side switch for driving 2 parallel NTBLS0D8N08XTXG MOSFETs. Please, find attached schematics below:

Then, we replace R8 and C16 for managing inrush current in our load: CLOAD = 1500uF, I startup = 80 mA @ 5V. After startup, our load can demand up to 250A peaks. We used your SOA calculator Excel sheet for calculating these values and we have tried 2 different configs: R8 = 470 kOhms, C16 = 220 nF, C18 = 4.7 uF and R8 = 100 kOhms, C16 = 440 nF, C18 = 4.7 uF.

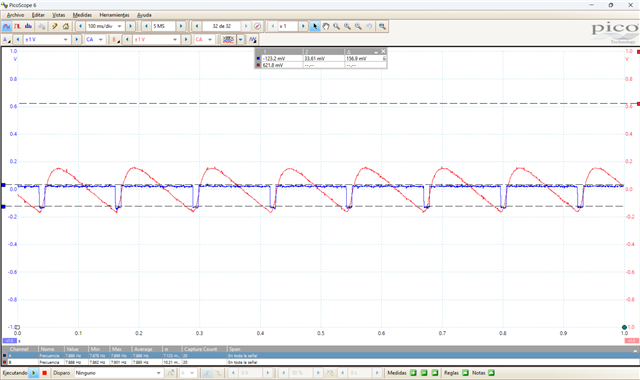

With any of these configs, we get VMOTOR drops when Iout is 35A or higher. Below you can see Vs and Vgate traces in AC coupling. As you can see, Vs (blue trace) perfectly follows Vgate (red trace):

After some time and by increasing the load, MOSFETs get shortcircuited (all their pins), probably due to these instant interruptions at high load. I have also checked FLT_I signal and it doesn't show any error. It doesn't follow neither Vs nor Vgate.

My question is: What could cause these voltage drops at Vgate at high loads?.

Kind regards.

My question is: what could cause this voltage drops at Vgate?