Other Parts Discussed in Thread: CSD19538Q2,

Tool/software:

Hello,

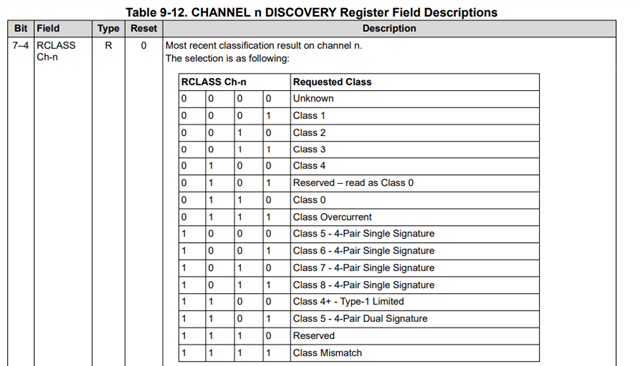

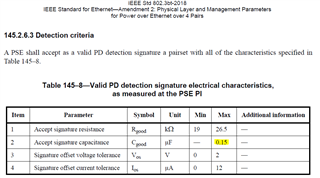

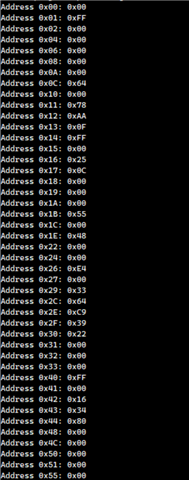

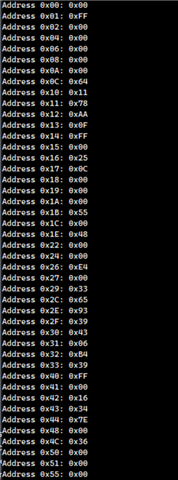

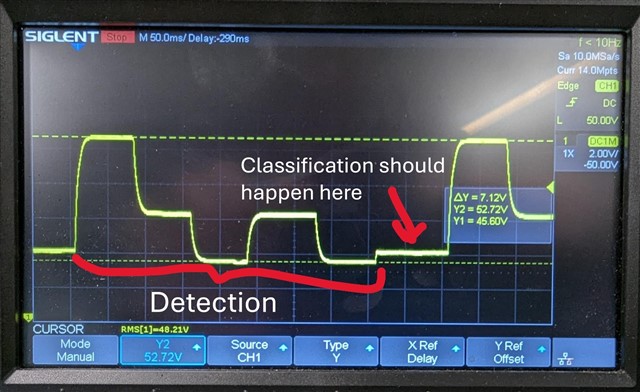

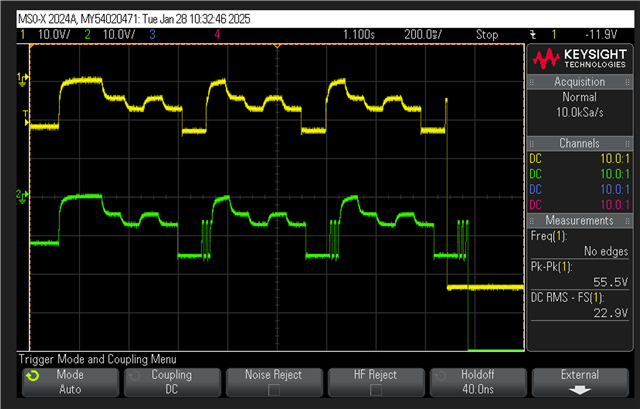

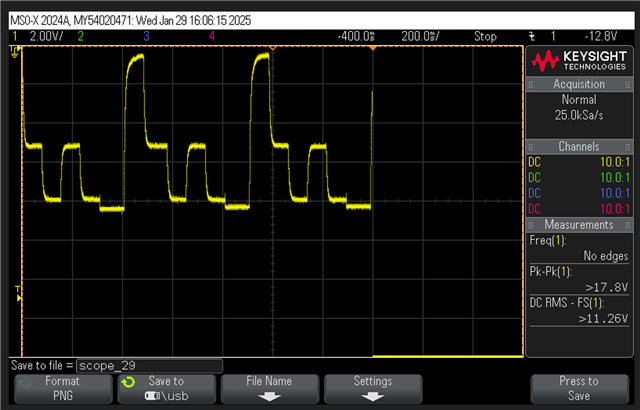

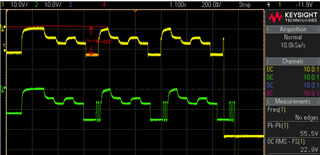

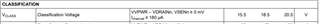

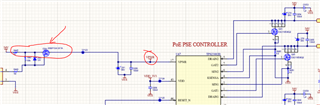

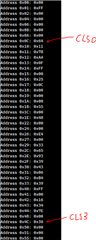

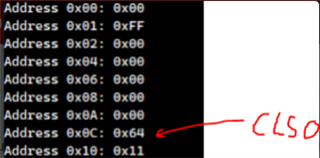

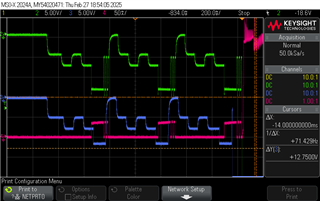

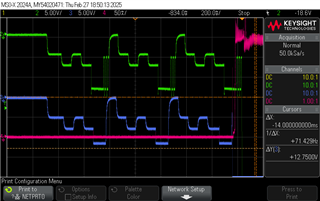

We're running into an issue with our TPS23882B PSE regarding classification in semi-auto mode. Our PD is supposed to classify at class 4, but when we plug it into our board, it's consistently classifying at class 0. Detection is working as expected.

We have the eval kit for the TPS23882B, and when we plug the PD into that, it's classifying properly at class 4, even when using the same register settings. This leads us to believe that there may be an issue with our PSE configuration.

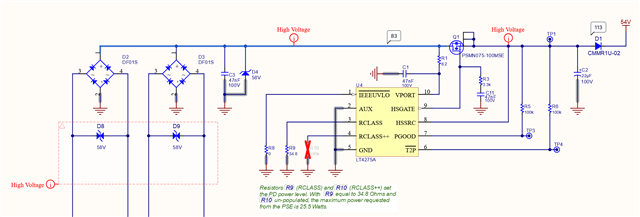

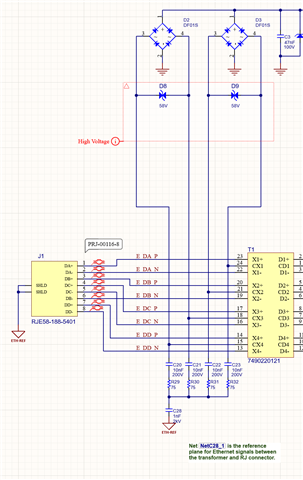

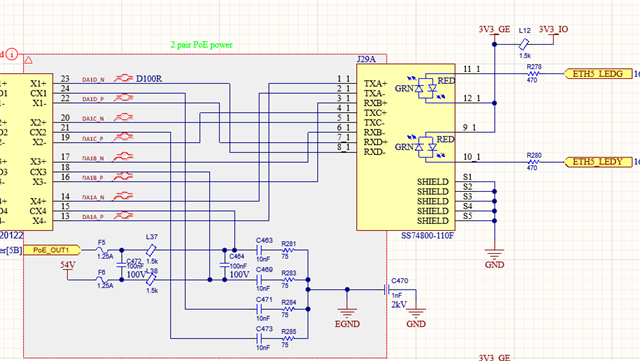

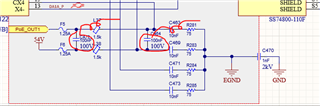

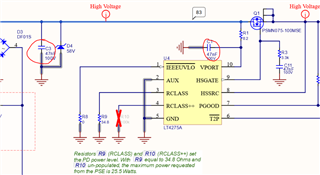

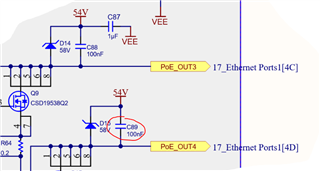

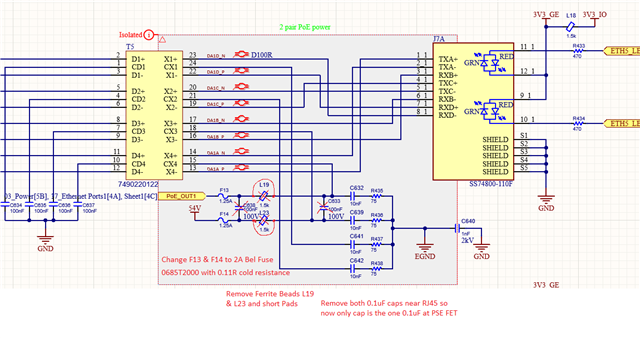

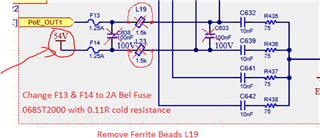

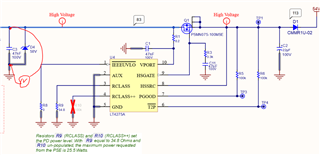

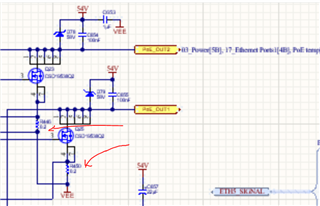

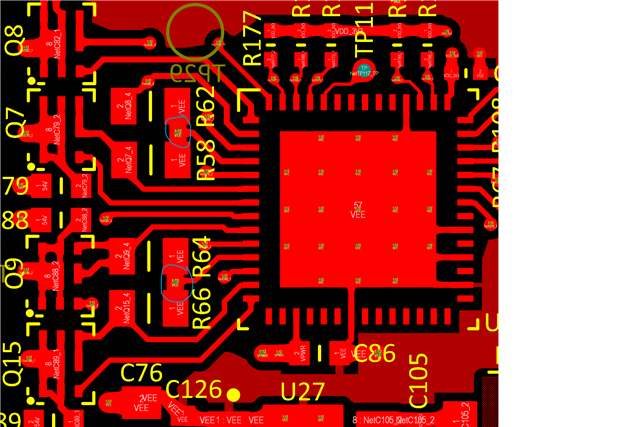

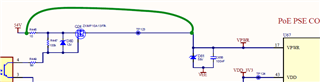

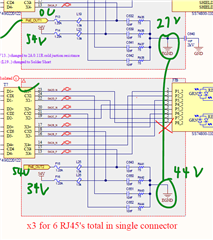

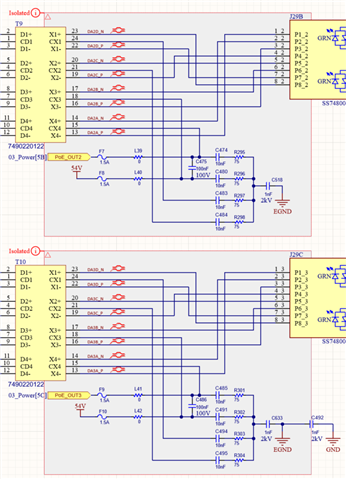

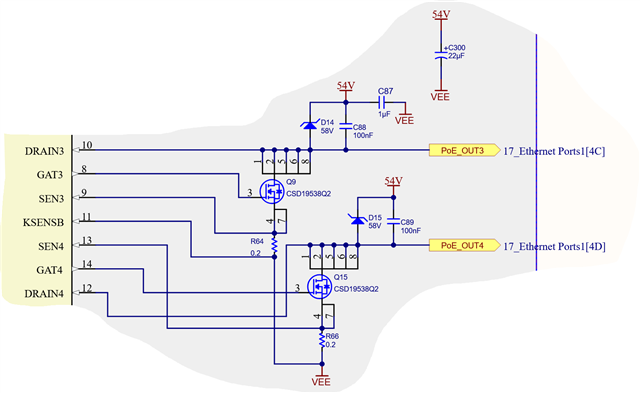

I've attached an excerpt from our schematic that shows how each pair of PoE ports are wired up to the PSE:

Any idea what may be going on that's causing the PD to not classify properly? Please let me know if more information is needed.