Tool/software:

Hi,

This is a continuation of the previous question. Please refer to the related threads before reading this post.

I took measures to slow down the rise of VDDIO using a power-on delay circuit (CR time constant circuit, etc.) so that it is within the range of the data sheet specifications.

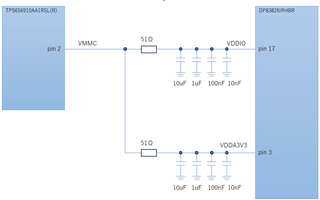

The CR time constant circuit (circuit shown below) meets the slew rate regulations of the power supply regulations, but when the consumption current (MAX 55mA) listed on page 14 of the DP83826 datasheet flows, a large voltage drop occurs at the 51Ω part and VDDIO / VDDA3V3 cannot be maintained at 3.3V.

I would appreciate it if you could suggest any other measures.

Thanks,

Conor