Other Parts Discussed in Thread: PMP23431

Tool/software:

Hi,

This post is the continuation of a previously asked question. Refer here: UCC28730-Q1: HV startup - Power management forum - Power management - TI E2E support forums

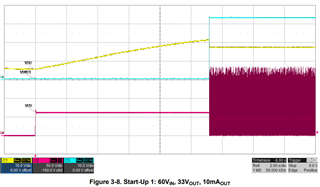

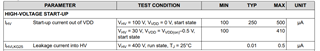

Datasheet mentions that the HV start-up current requirement is 250uA to charge the Vdd capacitor above UVLO threshold.

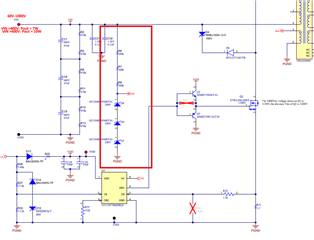

I am planning to implement a start-up circuit similar to the one provided in the reference design: PMP23431.1. Attached below is the image.

What happens if the HV start-up current provided is less than 250uA?

Will there just be a delay in the start-up as the Vdd capacitor is charged slowly? Or any other effects to reducing the HV start-up current below 250uA?

The reason for this query is that we are planning to operate the controller from 50V. This requires a HV resistance of (50V-30V)/250uA = 80kOhm, where 30V is the minimum ON voltage required at the HV pin.

But maximum voltage at the input can go up to 1700V for my application. This causes the power dissipated in the resistors as well as the zener to be very high at 1700V.

Please let me know if it's okay to provide a HV start-up current lesser than the limit mentioned in the datasheet.

Thanks

Ponkamali P