Tool/software:

Hello,

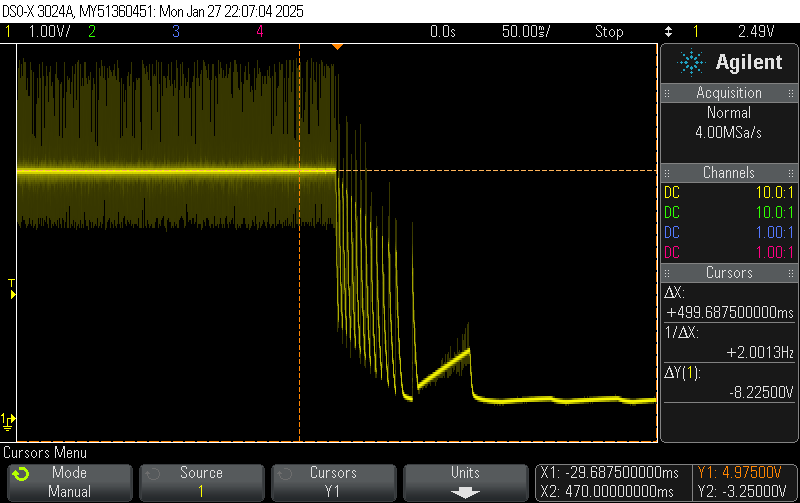

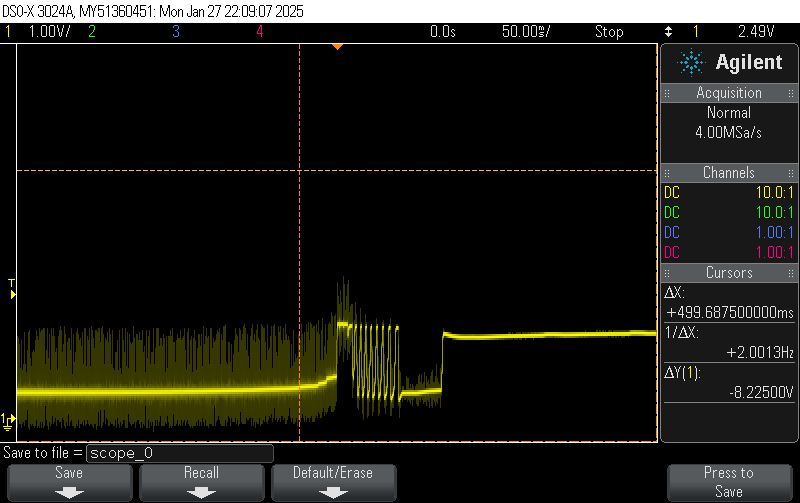

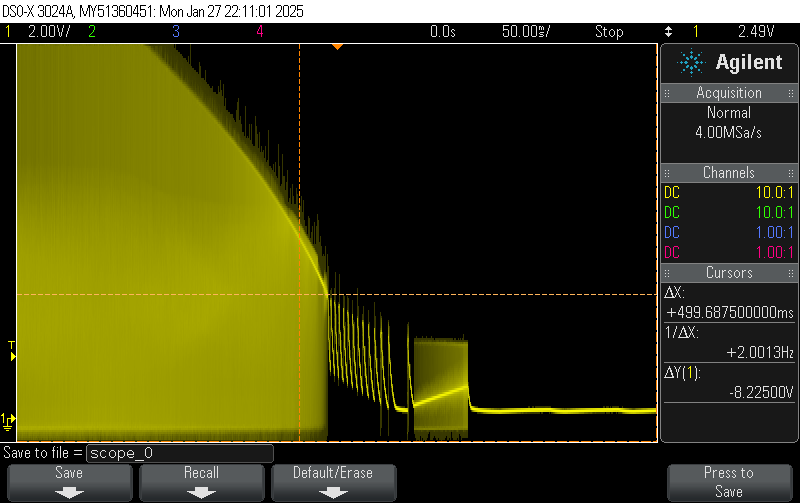

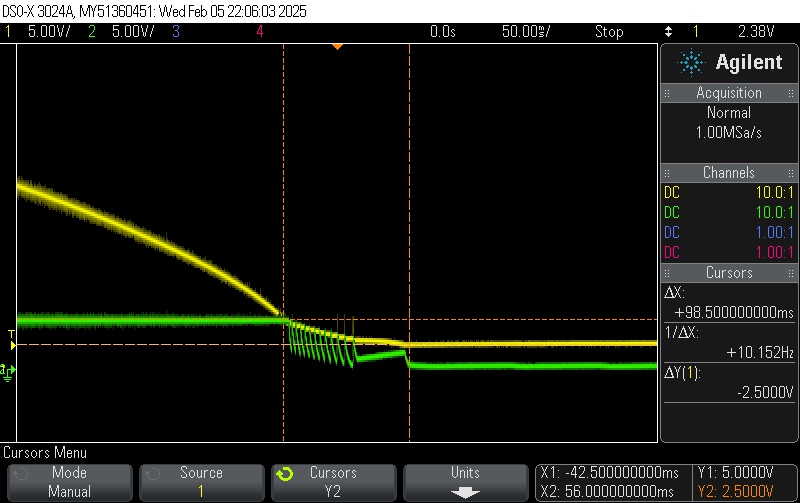

I am experiencing oscillations in my circuit using the TPS54160ADRCR DC/DC converter. The oscillations have a frequency of approximately 200 Hz and last for about 20 cycles. These oscillations occur specifically during shutdown when the input 24VDC drops.

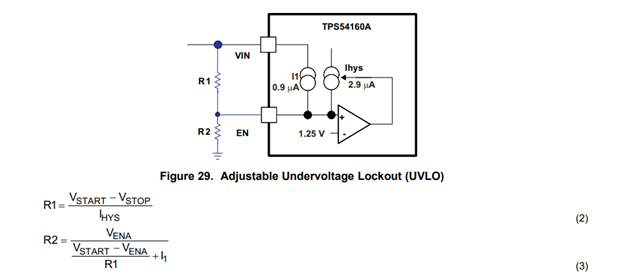

After simulating my design with TI Webench, I discovered that several component values in my current setup are out of the recommended range. Specifically:

- Output Capacitors: I currently have a 1µF capacitor in parallel with a 22µF capacitor. The datasheet recommends a minimum of 25.3µF to maintain output voltage regulation during unload transients. Webench suggests using two 47µF capacitors.

- Inductor: The current value is 3.3µH.

- Input Capacitor: The current value is 1µF.

These oscillations are affecting downstream components, such as the regulators to 3.3V, and may be causing damage to the final op-amp and other components.

I am attaching the schematics of this relevant part of the design for reference. Could the incorrect values of these components be the source of the oscillations I am observing during shutdown?

Thank you for your assistance.