Tool/software:

Hi,

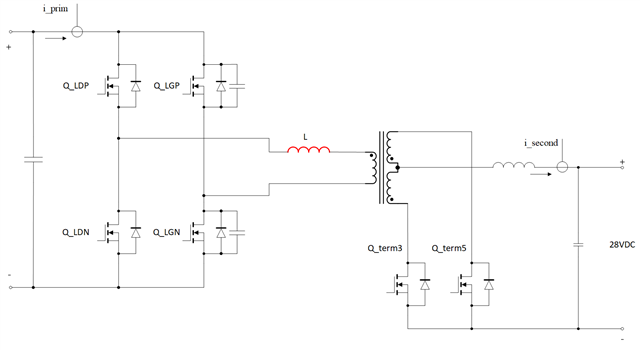

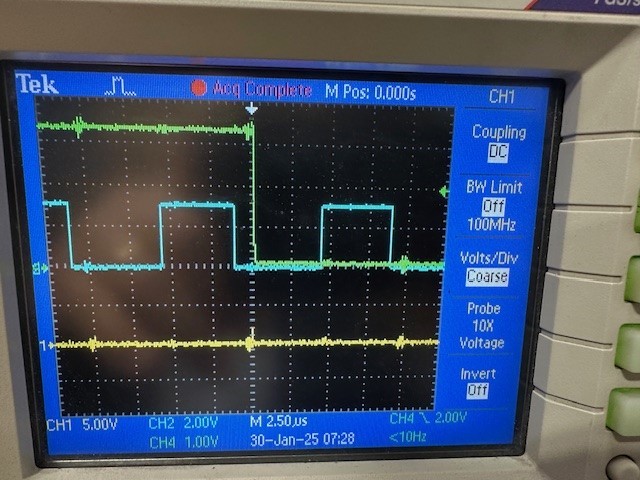

We have been using UCC21750 for a long time without any issues. Recently we use it in a synchronous rectifier circuit. First we disabled the MOSFETs driven by the driver chip, but we still see FLT pin going low. This is strange since the PWM is always low.

Are there any other reasons why FLT can go low even when the PWM is always low?

Thanks.