Tool/software:

To calcualte the Switch timings i search for additional information for the internal high side driver.

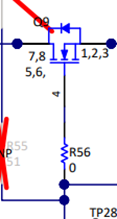

Inside the pin equivalent diagram the internal fets to switch "ON" the FETs aer shown. What is the resitance value of this drivers.

What is the minimum series (gate) resitance in sereis to the CHG and DSG pin to drive the FETs? Can I place 0R without damaging the BQ chip?

I know fast switching has other issues but i would like to understand the maximum possible what can be provided by the BQ chip.

Thanks

BR