Other Parts Discussed in Thread: TPS65994BH

Tool/software:

Hi TI team,

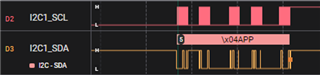

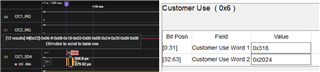

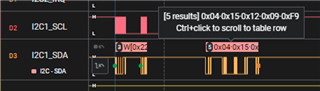

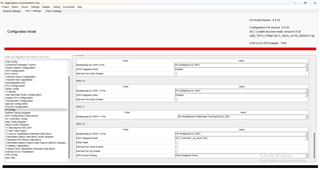

As title, I tried to use customization tool to disable all of the values for interrupt mask for I2C1 & I2C2 but also failed, but IO Config setting Pin Multiplexed to GPIO and Disable was OK. please help to check the pjt file, thanks.