Hi,

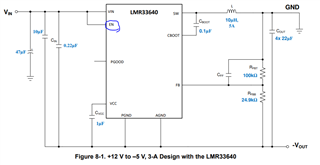

We are designing a negative power supply using the TI LMR33620 and are implementing external UVLO as described in the datasheet. However, we have some concerns regarding the applicability of the UVLO resistor calculation formula provided in the documentation.

Our Understanding & Concerns:

-

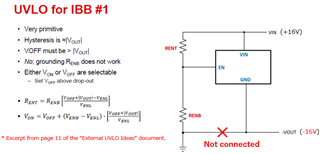

Applicability of the Existing UVLO Calculation for Negative Power Supply

- The formula given in the datasheet appears to be designed for positive power supply configurations.

- In our negative power supply design:VIN = 16V, VON = 15V, RENB = 10kΩ, VEN-H = 1.231V, Vout = -16V

- We are concerned whether the existing formula can be directly applied to a negative power rail.

-

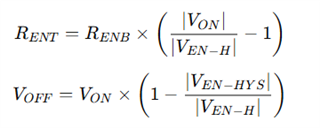

Modified UVLO Calculation for Negative Power Supply

- Based on our understanding, the calculation should account for the absolute values of V_ON and V_EN-H to ensure proper resistor divider operation.

- We derived the following modified formula for negative voltage UVLO:

- Could you confirm if this adjustment is correct for a negative power supply application?

- Can the UVLO resistor calculation from the datasheet be directly applied to negative power supply designs?

- If not, could you provide the correct formula or recommended approach for UVLO configuration in a negative voltage system?

Thanks,

Conor