Tool/software:

Hi,

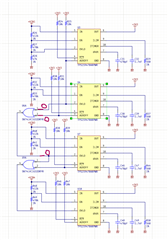

I am trying to make a priority power mux. I have seen the suggestions on the forum TPS25947: looking for a power mux solution - Power management forum - Power management - TI E2E support forums .

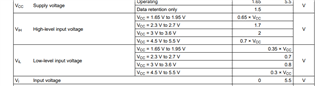

However, my implementation doesn't work. When I supply +VIN1 and +VIN2, it works. However, +VIN3 and +VIN4 don't work. I measured the U6A pin 1 and 2, I get 0V, hence 0V on the OVLO pin of U7.

In this case I assume that U7 doesn't supply +3V3, therefore the pull-ups don't work. Do you have any other suggestions?

Regards,

Caner